## Virginia Commonwealth University VCU Scholars Compass

Electrical and Computer Engineering Publications

Dept. of Electrical and Computer Engineering

2013

## Reliability of AlGaN/GaN high electron mobility transistors on low dislocation density bulk GaN substrate: Implications of surface step edges

N. Killat H. H. Wills Physics Laboratory, Nicole.Killat@bristol.ac.uk

M. Montes Bajo *H. H. Wills Physics Laboratory*

T. Paskova Kyma Technologies, North Carolina State University

See next page for additional authors

Follow this and additional works at: http://scholarscompass.vcu.edu/egre\_pubs Part of the <u>Electrical and Computer Engineering Commons</u>

Killat, N., Bajo, M. M., Paskova, T., et al., Reliability of AlGaN/GaN high electron mobility transistors on low dislocation density bulk GaN substrate: Implications of surface step edges. Applied Physics Letters, 103, 193507 (2013). Copyright © 2013 AIP Publishing LLC.

Downloaded from

http://scholarscompass.vcu.edu/egre\_pubs/8

This Article is brought to you for free and open access by the Dept. of Electrical and Computer Engineering at VCU Scholars Compass. It has been accepted for inclusion in Electrical and Computer Engineering Publications by an authorized administrator of VCU Scholars Compass. For more information, please contact libcompass@vcu.edu.

## Authors

N. Killat, M. Montes Bajo, T. Paskova, K. R. Evans, J. Leach, X. Li, Ü. Özgür, Hadis Morkoç, K. D. Chabak, A. Crespo, J. K. Gillespie, R. Fitch, M. Kossler, D. E. Walker, M. Trejo, G. D. Via, J. D. Blevins, and M. Kuball

## Reliability of AlGaN/GaN high electron mobility transistors on low dislocation density bulk GaN substrate: Implications of surface step edges

N. Killat,<sup>1,a)</sup> M. Montes Bajo,<sup>1</sup> T. Paskova,<sup>2,3,b)</sup> K. R. Evans,<sup>2</sup> J. Leach,<sup>2,4,b)</sup> X. Li,<sup>4</sup> Ü. Özgür,<sup>4</sup> H. Morkoç,<sup>4</sup> K. D. Chabak,<sup>5</sup> A. Crespo,<sup>5</sup> J. K. Gillespie,<sup>5</sup> R. Fitch,<sup>5</sup> M. Kossler,<sup>5</sup> D. E. Walker,<sup>5</sup> M. Trejo,<sup>5</sup> G. D. Via,<sup>5</sup> J. D. Blevins,<sup>5</sup> and M. Kuball<sup>1,a)</sup> <sup>1</sup>Center for Device Thermography and Reliability (CDTR), H.H. Wills Physics Laboratory, Tyndall Avenue, Bristol BS8 1TL, United Kingdom <sup>2</sup>Kyma Technologies, Inc., Raleigh, North Carolina 27617, USA <sup>3</sup>Materials Science and Engineering Department, North Carolina State University, Raleigh, North Carolina 27695, USA <sup>4</sup>Electrical and Computer Engineering Department, Virginia Commonwealth University, Richmond, Virginia 23284, USA <sup>5</sup>Air Force Research Laboratory, Wright-Patterson Air Force Base, Dayton, Ohio 45433, USA

(Received 30 September 2013; accepted 22 October 2013; published online 6 November 2013)

To enable gaining insight into degradation mechanisms of AlGaN/GaN high electron mobility transistors, devices grown on a low-dislocation-density bulk-GaN substrate were studied. Gate leakage current and electroluminescence (EL) monitoring revealed a progressive appearance of EL spots during off-state stress which signify the generation of gate current leakage paths. Atomic force microscopy evidenced the formation of semiconductor surface pits at the failure location, which corresponds to the interaction region of the gate contact edge and the edges of surface steps. © 2013 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4829062]

Recent advances in GaN high electron mobility transistor (HEMT) manufacturing have opened the way to a wide range of applications in the radar and communication sectors, as well as to power switching applications. Despite the impressive performance of state-of-the-art AlGaN/GaN HEMTs, in particular for high frequency, high power operation,<sup>1</sup> the question about device reliability remains not fully explored. The reliability issues often result in a de-rating of the devices in order to fulfil the reliability standard, therefore, not taking advantage of the full potential of the GaN device system. Understanding the physical mechanisms underlying the degradation phenomena and their correlation with structural and point defects within the semiconductor is crucial for the further improvement of device reliability. In particular, off-state degradation in AlGaN/GaN HEMTs on SiC substrate has been proposed to be linked to the generation of percolation paths via defects in the AlGaN barrier<sup>2</sup> or threading dislocations in the device epilayers.<sup>3</sup> However, up to date it is still unclear, whether there remain any further, yet unknown, degradation mechanisms, which can play a detrimental role for device reliability in off-state operation.

Bulk-GaN substrate availability has improved significantly over the last years with the steady progress in the development of hydride vapor phase epitaxy (HVPE)<sup>4</sup> and more recently of ammonothermal growth,<sup>5</sup> making these substrates more readily available. Therefore, bulk-GaN substrates are receiving cumulative attention as the potential substrate of choice for future GaN devices, although complete fabrication of GaN-on-GaN electronic devices may not be fully optimized yet. The absence of the nucleation layer, which is needed for the growth of device structures on SiC or Si substrates, as well as the rather high thermal conductivity of the bulk GaN substrate itself makes this device concept thermally competitive to GaN-on-SiC.<sup>6</sup> Most importantly for this work, however, GaN-on-GaN structures exhibit several orders of magnitude lower dislocation densities than GaN-on-SiC,<sup>7–9</sup> removing one of the potential device degradation contribution. These structures are therefore ideally suited for studying device degradation significantly less influenced by threading dislocations. In this work, we explore the impact of step edges in the device epilayers on off-state AlGaN/GaN HEMT degradation by means of electrical device characterization, electroluminescence (EL) imaging, and atomic force microscopy (AFM).

AlGaN/GaN HEMTs were grown by low-pressure metal organic vapor phase epitaxy (MOVPE) on a 500- $\mu$ m-thick semi-insulating bulk-GaN substrate with a Fe-doping concentration of  $3 \times 10^{18}$  cm<sup>-3</sup>. The GaN substrates were grown by HVPE, achieving a dislocation density as low as  $\sim 10^5$  cm<sup>-2</sup>.<sup>7</sup> The HEMT structures consisted of a 2- $\mu$ m-thick unintentionally doped GaN layer, an 18-nm-thick AlGaN barrier layer (25% Al content), and a 2-nm-thin GaN cap layer. Standard ohmic contacts were used for the source and the drain, and a standard Schottky contact for the gate. Devices had a gate length of 0.25  $\mu$ m, a gate width of 2 × 150  $\mu$ m, and a source-drain distance of 2.5  $\mu$ m. All devices were passivated with a 100-nm-thick SiN<sub>x</sub> layer deposited by plasma-enhanced chemical vapor deposition (PECVD). More details on the devices can be found in Ref. 5.

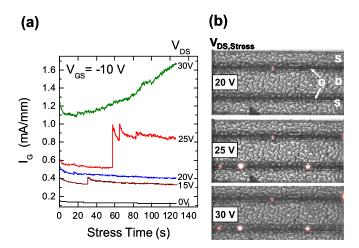

The GaN-on-GaN HEMTs were step-stressed in off-state at a gate-source voltage  $V_{GS} = -10$  V, about three times the threshold voltage, while the drain-source voltage  $V_{DS}$  was increased in 5 V steps from 0 to 30 V, spending 2 min at each stress step. During device stress, EL images were acquired

<sup>&</sup>lt;sup>a)</sup>Authors to whom correspondence should be addressed. Electronic addresses: Nicole.Killat@bristol.ac.uk and Martin.Kuball@bristol.ac.uk.

<sup>&</sup>lt;sup>b)</sup>This research was performed while T. Paskova was at Kyma Technologies, Inc., Raleigh, North Carolina 27617, USA and while J. Leach was at Virginia Commonwealth University, Richmond, North Carolina 27695, USA.

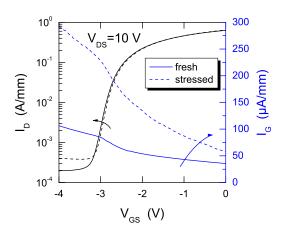

FIG. 1. Transfer characteristics of an AlGaN/GaN HEMT on bulk GaN substrate before and after off-state step stress up to  $V_{DS} = 30$  V and at  $V_{GS} = -10$  V.

using an astronomy-grade charged-coupled device (CCD) camera combined with a microscope and a  $50 \times (NA = 0.5)$  objective. The gate current  $I_G$  was simultaneously recorded during stress of the devices. DC characteristics of the devices were measured before and after stress to monitor the effect of the off-state stress on the device performance.

Figure 1 depicts the transfer characteristics of a representative  $2 \times 150$ -µm-wide AlGaN/GaN HEMT on bulk-GaN substrate before and after off-state stress. The most apparent observation is the increase in gate leakage current due to off-state stress, which also results in an increase in sub-threshold drain current. Figure 2(a) shows the evolution of the gate current during off-state step stress. For each stress step, the gate current  $I_G$  initially decreases over time, consistent with what has been reported previously, e.g., on GaN-on-SiC devices.<sup>10</sup> For  $V_{DS} > 15$  V,  $I_G$  experiences several abrupt increases during the stress steps. These gate current jumps coincide with the progressive appearance of EL spots near the drain-side edge of the gate contact, as illustrated in Figure 2(b). The EL spots indicate the location of generated gate current leakage paths which electrically connect the

FIG. 2. Off-state step stress of a  $2 \times 150$ -µm-wide HEMT at  $V_{GS} = -10$  V and with  $V_{DS}$  from 0 to 30 V: (a) Gate current during Off-state stress; (b) EL images at the end of each stress step, acquired with the CCD camera at 1 s integration time. The EL images are overlaid with white light images of the devices.

gate electrode or in general the device surface through the AlGaN barrier layer with the AlGaN/GaN channel. A similar observation, i.e., the appearance of EL spots and their correlation with the gate current evolution, has been reported for GaN-on-SiC HEMTs during off-state stress.<sup>2,10–12</sup> For a  $V_{DS}$  of 30 V and above,  $I_G$  showed a monotonous increase over time, which may indicate the onset of an additional wear-out mechanism, as this was not related to the occurrence of further EL spots. Here, we focus on the early-stage degradation of the devices.

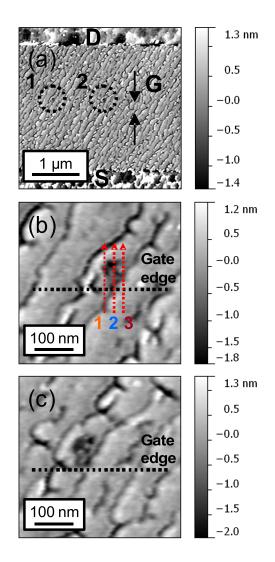

To gain insight into the physical mechanisms of the device degradation, the  $SiN_x$  passivation layer and contacts were removed after the completion of the electrical stressing procedure by wet chemical etching as in Refs. 11 and 13. AFM images were then acquired from the exposed semiconductor surface. An AFM image taken from a region of the device where EL spots were present (Figure 3) shows pits near the drain side of the gate edge. A careful overlay of the AFM and EL images reveals that surface pits appear at the

FIG. 3. AFM image of a GaN-on-GaN HEMT after removal of the contacts and passivation: (a) AFM image of the source-drain gap, where the location of the removed source, drain, and gate contacts is indicated, as well as the presence of two failure-spot-related surface pits; (b) and (c) Detailed AFM images of the pits labeled as 1 and 2 in (a), respectively. The former location of the drain-side edge of the gate is indicated as dashed line. The numbered arrows in (b) refer to the AFM profiles in Figure 4.

This article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP 128 172 48 58 Op; Mon. 30 Mar 2015 18:13:01

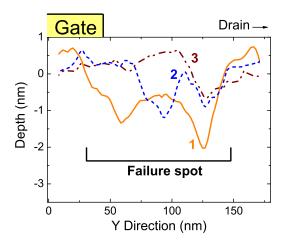

exact same locations where the EL spots progressively emerged during stress, similar to what has been reported for GaN-on-SiC.<sup>11</sup> The geometry of these pits (Figures 3(b) and 3(c)), and also the internal structure they exhibit (Figure 4), is rather irregular and does not feature a faceted, symmetric V-type shape. This may suggest that the pit formation mechanism may not directly result from a physical material cracking as a consequence of the inverse piezoelectric effect,<sup>14</sup> but is probably a time-accumulated effect caused by electrochemical reactions on the device surface.<sup>15</sup> The stress-generated pits, as observed in the AFM images, typically feature a lateral dimension of about 80 nm and are on average 1 nm deep (see Figure 4).

The dislocation density in the device epilayers is several orders of magnitude lower than in state-of-the-art GaNon-SiC devices. Indeed, the lack of surface step termination points observed in the AFM maps denotes the virtual absence of screw-type dislocations in the device epilayers.<sup>16,17</sup> In principle, if threading dislocations, which evidently can be crucial for GaN device reliability,<sup>3</sup> were the only mechanism triggering the off-state degradation of AlGaN/GaN HEMTs, no significant degradation would be expected for GaN-on-GaN HEMTs. Consequently, one could argue that percolated current paths through trap states in the AlGaN barrier layer may play the dominant role for the devices studied here. Nevertheless, considering the spatially random nature of trap generation, a statically random distribution of the failure sites along the gate edge would be expected.

As displayed in Figure 3, we observed ~2-nm-high growth steps on the surface of the devices with relatively rough and non-uniform step edges, i.e., the step edges are ill-defined and reveal numerous grooves. About 85% of the total number of observed pits appear to emerge from a point where the drain-edge of the gate contact crosses one of these step edges, spreading towards the drain. Examples are illustrated in Figures 3(b) and 3(c). The edges of growth terraces may inherit a higher risk of defect generation due to the high density of dangling bonds that may result in surface states.<sup>18</sup> This is consistent with recently demonstrated enhanced surface trapping at step edges in AlGaN/GaN HEMTs,<sup>19</sup> locally

FIG. 4. AFM profiles along the direction of the three arrows indicated in Figure 3(b). The former location of the gate contact is indicated at the top of the graph.

impacting the electric field near the gate edge. Step edges have also been reported in as-grown structures to increase gate leakage through the barrier layer.<sup>20</sup> When the drain edge of the gate contact, where the highest electric field occurs, crosses a step edge, these sites may become much more vulnerable to off-state degradation. In contrast, one would expect point defects and generated traps in the AlGaN layer to be distributed randomly along the gate edge, i.e., not correlated to the step edges or any other surface feature. Consequently, point defects alone cannot present the cause for off-state degradation under consideration here. This supports the link of step edges and related surface defects with a possible triggering mechanism for the emergence of gate current leakage paths in GaN HEMTs, underlining that the surface microstructure plays a key role for GaN device degradation. Optimization of the surface morphology of GaN-on-GaN may therefore be an important factor to consider for electronic device developments on bulk-GaN substrate growth.

In conclusion, off-state stress of GaN-on-GaN HEMTs was used to demonstrate that step edges and associated electronic trap states can trigger the generation of failure spots in the device epilayers. The surface microstructure therefore plays a key role for off-state degradation in GaN devices. Further advancements in GaN-on-GaN growth minimizing the impact of step edges and further epilayer optimizations may be a way forward towards high reliability GaN electronic devices.

We acknowledge the financial support from the EPSRC (EP/H011366/1) and ONR Global (N00014-08-1-1091) through the DRIFT program (monitored by Dr. Paul Maki).

- <sup>1</sup>D. Runton, B. Trabert, J. Shealy, and R. Vetury, IEEE Microw. Mag. 14, 82 (2013).

- <sup>2</sup>M. Meneghini, A. Stocco, M. Bertin, D. Marcon, A. Chini, G. Meneghesso, and E. Zanoni, Appl. Phys. Lett. **100**, 033505 (2012).

- <sup>3</sup>M. Ťapajna, S. W. Kaun, M. H. Wong, F. Gao, T. Palacios, U. K. Mishra, J. S. Speck, and M. Kuball, Appl. Phys. Lett. **99**, 223501 (2011).

- <sup>4</sup>T. Paskova and K. R. Evans, IEEE J. Sel. Top. Quantum Electron. **15**, 1041 (2009).

- <sup>5</sup>R. Dwiliński, R. Doradziński, J. Garczyński, L. P. Sierzputowski, A. Puchalski, Y. Kanbara, K. Yagi, H. Minakuchi, and H. Hayashi, J. Cryst. Growth **310**, 3911 (2008).

- <sup>6</sup>N. Killat, M. Montes, J. W. Pomeroy, T. Paskova, K. R. Evans, J. Leach, Ü. Özgür, H. Morkoç, K. D. Chabak, J. K. Gillespie, R. Fitch, M. Kossler, D. E. Walker, M. Trejo, G. D. Via, J. D. Blevins, and M. Kuball, IEEE Electron Device Lett. **33**, 366 (2012).

- <sup>7</sup>T. Paskova, D. A. Hanser, and K. R. Evans, Proc. IEEE 98, 1324 (2010).

- <sup>8</sup>M. Ťapajna, N. Killat, J. Moereke, T. Paskova, K. Evans, J. Leach, X. Li, Ü. Özgür, H. Morkoç, K. Chabak, A. Crespo, J. Gillespie, R. Fitch, M. Kossler, D. Walker, M. Trejo, G. Via, J. D. Blevins, and M. Kuball, IEEE Electron Device Lett. **33**, 1126 (2012).

- <sup>9</sup>C. Mion, J. F. Muth, E. A. Preble, and D. Hanser, Appl. Phys. Lett. **89**, 092123 (2006).

- <sup>10</sup>D. Marcon, D. Kauerauf, F. Medjdoub, J. Das, M. Van Hove, P. Srivastava, K. Chen, M. Leys, R. Mertens, S. Decoutere, G. Meneghesso, E. Zanoni, and G. Borghs, *IEEE International Electron Device Meeting (IEDM)* (IEEE, 2010), pp. 20.3.1–20.3.4.

- <sup>11</sup>M. Montes Bajo, C. Hodges, M. J. Uren, and M. Kuball, Appl. Phys. Lett. 101, 033508 (2012).

- <sup>12</sup>C. Hodges, N. Killat, S. W. Kaun, M. H. Wong, F. Gao, T. Palacios, U. K. Mishra, J. S. Speck, D. Wolverson, and M. Kuball, Appl. Phys. Lett. 100, 112106 (2012).

- <sup>13</sup>P. Makaram, J. Joh, J. A. Del Alamo, T. Palacios, and C. V. Thompson, Appl. Phys. Lett. **96**, 233509 (2010).

This article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP

- <sup>14</sup>J. Joh and J. del Alamo, in Proc. IEEE International Devices Meeting, IEDM '06, San Francisco, USA, 415 (2006).

- <sup>15</sup>F. Gao, B. Lu, L. Li, S. Kaun, J. S. Speck, C. V. Thompson, and T. Palacios, Appl. Phys. Lett. **99**, 223506 (2011).

- <sup>16</sup>R. F. Davis, S. M. Bishop, S. Mita, R. Collazo, Z. J. Reitmeier, and Z. Sitar, AIP Conf. Proc. 916, 520 (2007).

- <sup>17</sup>B. Heying, E. J. Tarsa, C. R. Elsass, P. Fini, S. P. DenBaars, and J. S. Speck, J. Appl. Phys. 85, 6470 (1999).

- <sup>18</sup>M. H. Xie, S. M. Seutter, W. K. Zhu, L. X. Zheng, H. Wu, and S. Y. Tong, Phys. Rev. Lett. 82(13), 2749 (1999).

- <sup>19</sup>N. Killat, M. J. Uren, S. Kolluri, S. Keller, U. K. Mishra, and M. Kuball, in Proc. CS ManTech Conference, Boston, USA, 2012.

- <sup>20</sup>B. Kim, D. Y. Moon, K. Joo, S. H. Park, S. Oh, G.-D. Lee, Y. Lee, Y. Nanishi, Y. Moon, Y. Park, and E. Yoon, in International Conference on Nitride Semiconductors 2013, Washington, DC, USA, 2013.