# Virginia Commonwealth University VCU Scholars Compass

**Electrical and Computer Engineering Publications**

Dept. of Electrical and Computer Engineering

2011

### Charge storage characteristics of ultra-small Pt nanoparticle embedded GaAs based non-volatile memory

Reginald Jeff University of Missouri

M Yun University of Missouri

B Ramalingam

North Carolina State University

See next page for additional authors

Follow this and additional works at: https://scholarscompass.vcu.edu/egre\_pubs

Part of the Electronic Devices and Semiconductor Manufacturing Commons

#### Downloaded from

https://scholarscompass.vcu.edu/egre\_pubs/204

This Article is brought to you for free and open access by the Dept. of Electrical and Computer Engineering at VCU Scholars Compass. It has been accepted for inclusion in Electrical and Computer Engineering Publications by an authorized administrator of VCU Scholars Compass. For more information, please contact libcompass@vcu.edu.

| <b>Authors</b><br>Reginald Jeff, M Yun, B Ramalingam, B Lee, V Misra, Gregory Edward Triplett, and Shubhra Gangopadhyay |

|-------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                         |

|                                                                                                                         |

|                                                                                                                         |

|                                                                                                                         |

|                                                                                                                         |

|                                                                                                                         |

|                                                                                                                         |

|                                                                                                                         |

|                                                                                                                         |

|                                                                                                                         |

|                                                                                                                         |

|                                                                                                                         |

|                                                                                                                         |

|                                                                                                                         |

## Charge storage characteristics of ultra-small Pt nanoparticle embedded GaAs based non-volatile memory

R. C. Jeff, M. Yun, B. Ramalingam, B. Lee, V. Misra, G. Triplett, and S. Gangopadhyay

Citation: Appl. Phys. Lett. 99, 072104 (2011); doi: 10.1063/1.3625426

View online: https://doi.org/10.1063/1.3625426

View Table of Contents: http://aip.scitation.org/toc/apl/99/7

Published by the American Institute of Physics

#### Articles you may be interested in

A silicon nanocrystals based memory

Applied Physics Letters 68, 1377 (1996); 10.1063/1.116085

Nonvolatile nano-floating gate memory devices based on pentacene semiconductors and organic tunneling insulator layers

Applied Physics Letters **96**, 033302 (2010); 10.1063/1.3297878

High density platinum nanocrystals for non-volatile memory applications

Applied Physics Letters 92, 073102 (2008); 10.1063/1.2840188

Resistive switching of aluminum oxide for flexible memory

Applied Physics Letters 92, 223508 (2008); 10.1063/1.2939555

Charge storage characteristics of atomic layer deposited  $RuO_x$  nanocrystals

Applied Physics Letters 90, 253108 (2007); 10.1063/1.2749857

Sputter deposition onto ionic liquids: Simple and clean synthesis of highly dispersed ultrafine metal nanoparticles Applied Physics Letters **89**, 243117 (2006); 10.1063/1.2404975

# Charge storage characteristics of ultra-small Pt nanoparticle embedded GaAs based non-volatile memory

R. C. Jeff, Jr., <sup>1</sup> M. Yun, <sup>1</sup> B. Ramalingam, <sup>1</sup> B. Lee, <sup>2</sup> V. Misra, <sup>2</sup> G. Triplett, <sup>1,a)</sup> and S. Gangopadhyay <sup>1,b)</sup>

(Received 8 June 2011; accepted 23 July 2011; published online 15 August 2011)

Charge storage characteristics of ultra-small Pt nanoparticle embedded devices were characterized by capacitance-voltage measurements. A unique tilt target sputtering configuration was employed to produce highly homogenous nanoparticle arrays. Pt nanoparticle devices with sizes ranging from  $\sim$ 0.7 to 1.34 nm and particle densities of  $\sim$ 3.3–5.9 × 10<sup>12</sup> cm<sup>-2</sup> were embedded between atomic layer deposited and e-beam evaporated tunneling and blocking Al<sub>2</sub>O<sub>3</sub> layers. These GaAs-based non-volatile memory devices demonstrate maximum memory windows equivalent to 6.5 V. Retention characteristics show that over 80% charged electrons were retained after 10<sup>5</sup> s, which is promising for device applications. © 2011 American Institute of Physics. [doi:10.1063/1.3625426]

Si-based floating gate non-volatile memories<sup>1</sup> have experienced significant growth in mobile data storage applications. Even more, discrete nanocrystal/nanoparticle (metal) embedded devices are also attractive because of the lateral isolation of each storage site. Sub-2 nm platinum (Pt) nanoparticle embedded non-volatile memory devices with controllable (1–4.3 V) memory windows under low programming/erasing (P/E) voltages<sup>2</sup> were recently reported where nanoparticles smaller than 2 nm demonstrate Coulomb blockade effect.<sup>3</sup> In this study, we explore ultra-small Pt nanoparticle embedded GaAs metal-oxide-semiconductor (MOS) structures for operation at room temperature.

Replacing Si with GaAs offers unique performance capabilities, particularly for memory devices.<sup>4</sup> The charging effect, however, influences carrier leakage through the Al<sub>2</sub>O<sub>3</sub> and is sensitive to temperature (due to thermal excitation).<sup>5</sup> For GaAs memory devices, several issues include: (i) deposition of dielectric layers onto the GaAs surface and Fermi level pinning from high density surface states<sup>6</sup> and (ii) difficulty with producing high quality oxide/GaAs interfaces to allow controlled charge transfer, which is associated with native/deposited oxides at the GaAs surface. 7-9 Appropriately, efforts have included surface passivation and interfacial cleaning techniques to perfect the interface. 10-13 Atomic layer deposition (ALD) has also been employed to synthesize high-quality gate dielectrics onto GaAs and has shown suppressed interface trap densities with proper post-deposition annealing.<sup>14</sup> Here, we report charge storage characteristics of GaAs MOS structures with high-density ultra-small Pt nanoparticles between ALD tunneling and e-beam evaporated blocking Al<sub>2</sub>O<sub>3</sub> layers. The nanoparticle formation utilizes a unique tilted-target sputter (TTS) configuration producing low density and low energy metal atoms, from which highly homogenous Pt nanoparticles in the sub-2 nm range are observed. In TTS configuration, dimensions of Pt nanoparticles can be controlled by varying deposition time and power. Room temperature capacitance-voltage (C-V) and conductance-voltage (G-V) measurements show memory effects due to electron charging via Pt nanoparticles, which is in contrast to observations attributed to trapped sites between  $\mathrm{Al_2O_3}$  and  $\mathrm{GaAs}$ .

In this study, memory devices were fabricated using ptype GaAs (100) substrates. Fabrication steps include: wafer degreasing, wafer cleaning in HCl:H<sub>2</sub>O (1:5), sulfur passivation in NH<sub>4</sub>S<sub>2</sub> (40%–48% by weight in H<sub>2</sub>O) at room temperature, 3 nm thick ALD deposited Al<sub>2</sub>O<sub>3</sub> tunnel dielectric at 200 °C, post-deposition annealing using rapid thermal annealing in N<sub>2</sub> at 400 °C, and Pt nanoparticle deposition using TTS configuration. With TTS configured at 23.8° angle, deposition time and power were varied producing nanoparticle arrays with sizes  $\sim\!0.7\text{-}1.34$  nm and densities  $3.3\text{-}5.9\times10^{12}~\text{cm}^{-2}$ . Twenty nanometer thickAl<sub>2</sub>O<sub>3</sub> blocking layers were then deposited by e-beam evaporation, and H<sub>2</sub> annealed at 260 °C. Ti electrodes were then patterned using a shadow mask.

Pt nanoparticles were also deposited on  $Al_2O_3$  (5 nm) coated carbon grids for transmission electron microscopic (TEM) imaging (Figure 1). Nearly homogeneous particle arrays were obtained unlike that observed in other dewetting techniques. Particle size homogeneity can be attributed to shadowing effect caused by the angular flux and low energy metal atoms in the deposition regime for particle formation.

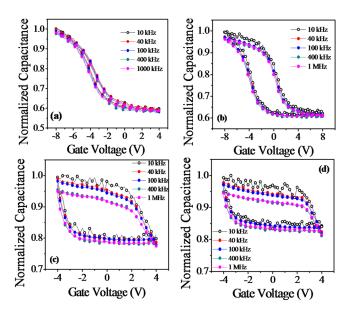

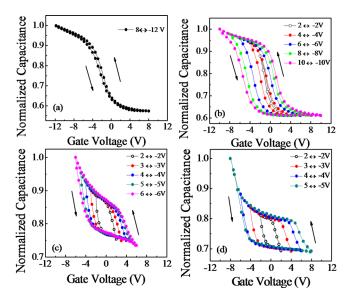

C-V measurements were executed under dark conditions with a voltage step of 0.1 V and a 30 mV ac signal at frequencies varying from 10 kHz to 1 MHz. Figure 2 shows the frequency dependent C-V curves of the control sample and the Pt nanoparticle embedded memory devices. This data are evident that the memory window was independent of frequency from 10 kHz to 1 MHz, indicating that the obtained charging effect originates from Pt nanoparticles, not the trapped states in Al<sub>2</sub>O<sub>3</sub> or Al<sub>2</sub>O<sub>3</sub>/GaAs interfaces. Figure 3 shows C-V curves of the control sample and the Pt

<sup>&</sup>lt;sup>1</sup>Department of Electrical and Computer Engineering, University of Missouri, Columbia, Missouri 65211, USA

<sup>&</sup>lt;sup>2</sup>Department of Electrical and Computer Engineering, North Carolina State University, Raleigh, North Carolina 27695, USA

<sup>&</sup>lt;sup>a)</sup>Electronic mail: triplettg@missouri.edu.

b) Electronic mail: gangopadhyays@missouri.edu.

FIG. 1. (Color online) TEM images and particle size distribution (inset) (a)  ${\sim}0.696\,$  nm nanoparticles, (b)  ${\sim}1.08\,$  nm nanoparticles, (c)  ${\sim}1.34\,$  nm nanoparticles.

nanoparticle embedded memory device under various sweeping gate voltages. Samples did not reach saturation in the accumulation region because of quantum mechanical tunneling from the ultra-thin tunneling layer. The control sample shows an approximate initial flatband voltage,  $V_{FB} = -4~V$  (and  $\sim 0.5~V$  negligible hysteresis), which is attributed to traps developed during fabrication of the two  $Al_2O_3$  layers.  $V_{FB}$  for the smallest nanoparticles varied with voltage sweep (Figure 3(b)), but for the purpose of measuring flatband shifting ( $\Delta V_{FB}$ ),  $V_{FB}$  was assumed to be -1.8~V at  $\pm 2~V$ . Counterclockwise hysteresis loops shown to indicate electron injection under positive voltage for P-modes and hole injec-

FIG. 2. (Color online) Normalized frequency dependent C-V curves of (a) control, (b)  ${\sim}0.696$  nm nanoparticles, (c)  ${\sim}1.08$  nmnanoparticles, (d)  ${\sim}1.34$  nm at frequencies 10 kHz to 1 MHz.

FIG. 3. (Color online) Normalized C-V curves of (a) control, (b)  $\sim$ 0.696 nm nanoparticles, (c)  $\sim$ 1.08 nmnanoparticles, (d)  $\sim$ 1.34 nm nanoparticles samples under different sweeping gate voltages.

tion under negative voltage for E-modes. Unlike 3–4 nm AuPd nanoparticle embedded metal-insulator-semiconductor field-effect transistors (MISFETs), <sup>10</sup> charge storage was demonstrated at room temperature due to high quality Al<sub>2</sub>O<sub>3</sub> tunneling layer and ultra-small particles.

Memory devices ( $\sim$ 1.08 nm and  $\sim$ 1.34 nm particle arrays) exhibited adverse initial charging effects, as shown in Figures 3(c) and 3(d). This demonstrates that larger particles produce initial charging due to weaker Coulomb blockade effect. Using an approximation for the self-capacitance (C) of a single nanoparticle, Coulomb charging energies,  $q^2/2C$  (where C is the self-capacitance 18), were calculated and ranged from  $\sim$ 170-320 meV.

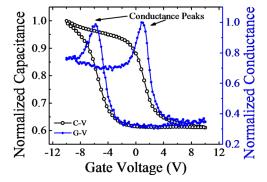

Although the Coulomb charging energies for all samples are above kT (25 meV), very thin tunnel layers increase leakage, thus requiring larger Coulomb blockade effect to confine charges. Figure 4 illustrates C-V and G-V curves for smaller nanoparticles at  $\pm 10$  V voltage sweep. Here, the conductance peaks are positioned close to  $V_{FB}$  in both forward/reverse directions. The hysteresis characteristics observed can be attributed to electrons trapped in or at the interface of the embedded Pt-nanoparticle. <sup>19</sup>

The change in  $\Delta V_{FB}$  was also calculated, where  $\Delta V_{FB}$  increased under both the P/E directions due to an increase in

FIG. 4. (Color online) C-V versus G-V curves for  $\sim$ 0.696 size nanoparticles ( $\pm$ 10 V bi-direction sweep).

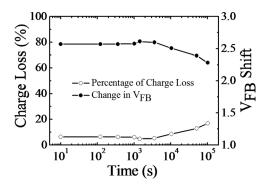

FIG. 5. Retention characteristics of the Pt nanoparticle embedded GaAs memory device.

Pt nanoparticle stored charges. The forward/reverse C-V sweeps also revealed that the maximum magnitude of charge storage effect was 6.5 V. Using the relationship,  $N = \frac{C_{ox}\Delta V_{FB}}{\sigma^A}$ , where N is the trapped charge density,  $C_{ox}$  is the accumulation capacitance, and A is device area, the maximum electron charge density ( $\sim 6.75 \times 10^{12} \text{ cm}^{-2}$ ) and particle density  $(\sim 3.294 \times 10^{12} \text{ cm}^{-2})$  was determined revealing that approximately two electrons are stored in or at the interface of a single Pt nanoparticle. The initial stressing for retention measurements confirms that electrons have been trapped in Pt nanoparticles. An initial loss of 6.3% was demonstrated after 10 s (due to back electron tunneling), and as illustrated in Figure 5, charge losses up to 16.8% of the initial charge values were observed after 105 s, which demonstrates the feasibility of these structures in non-volatile memory.

In summary, near homogenous ultra-small Pt nanoparticles between ALD and e-beam deposited Al<sub>2</sub>O<sub>3</sub> layers in GaAs MOS structures revealed a charge storage effect with a maximum flatband voltage shift of 6.5 V. Test structures demonstrated  $\sim 83\%$  retention after  $10^5$  s. These dielectric layers together with the use of ultra-small Pt nanoparticle could lead to room temperature operation of GaAs non-volatile memory applications.

This work was supported by the National Science Foundation under Grant No. GOALI-0523656.

<sup>1</sup>G. W. Burr, B. N. Kurdi, J. C. Scott, C. H. Lam, K. Gopalakrishnan, and R. S. Shenoy, IBM J. Res. Dev. 52, 449 (2008).

<sup>2</sup>M. Yun, D. W. Mueller, M. Hossain, V. Misra, and S. Gangopadhyay, IEEE Trans. Electron Devices 30, 1362 (2009).

<sup>3</sup>H. Tsuji, N. Arai, T. Matsumoto, K. Ueno, Y. Gotoh, K. Adachi, H. Kotaki, and J. Ishikawa, Appl. Sur. Sci. 239, 132 (2004).

<sup>4</sup>F. Sabri and D. G. Hasko, Appl. Phys. Lett. **74**, 2996 (1999).

<sup>5</sup>E. S. Kannan, G.-H. Kim, and D. A. Ritchie, Appl. Phys. Lett. **95**, 143506 (2009)

<sup>6</sup>H. C. Lin, G. Brammertz, K. Martens, G. de Valicourt, L. Negre, W.-E. Wang, W. Tsai, M. Meuris, and M. Heyns, Appl. Phys. Lett. 94, 153508 (2009).

<sup>7</sup>F. Gao, S. J. Lee, D. Z. Chi, S. Balakumar, and D. L. Kwong, Appl. Phys. Lett. 90, 252904 (2007).

<sup>8</sup>K. Martens, C. O. Chui, G. Brammertz, B. De Jaeger, D. Kuzum, M. Meuris, M. M. Heyns, T. Krishnamohan, K. Saraswat, H. E. Maes, and G. Groeseneken, IEEE Trans. Electron Devices 55, 547 (2008).

9S. Koveshnikov, W. Tsai, I. Ok, J. C. Lee, V. Torkanov, M. Yakimov, and S. Oktyabrsky, Appl. Phys. Lett. 88, 022106 (2006).

<sup>10</sup>H. Lu, L. L Sun, S. Din, M. Xu, D. W. Zhang, and L. Wang, Appl. Phys. Lett. 89, 152910 (2006).

<sup>11</sup>G. Brammertz, H. C. Lin, K. Martens, D. Mercier, S. Sioncke, A. Delabie, W. E. Wang, M. Caymax, M. Meuris, and M. Heyns, Appl. Phys. Lett. 93, 183504 (2009).

<sup>12</sup>R. Suri, D. J. Lichtenwalner, and V. Misra, Appl. Phys. Lett. **89**, 152910 (2006)

<sup>13</sup>C. L. Hinkle, A. M. Sonnet, M. Milojevic, F. S. Aguirre-Tostado, H. C. Kim, J. Kim, R. M. Wallace, and E. M. Vogel, Appl. Phys. Lett. 93, 113506 (2009).

<sup>14</sup>R. Suri, B. Lee, D. J. Lichtenwalner, N. Biawas, and V. Misra, Appl. Phys. Lett. 93, 193504 (2008).

<sup>15</sup>Z. Liu, C. Lee, V. Narayanan, G. Pei, and E. C. Kan, IEEE Trans. Electron Devices 49(9), 1606 (2002).

<sup>16</sup>R. Yu, H. Song, X.-F. Zhang, and P. Yang, J. Phys. Chem. B 109(15), 6940 (2005).

<sup>17</sup>J. Sune, P. Olivo, and B. Ricco, IEEE Trans. Electron Devices 39, 1732

<sup>18</sup>C.-H. Cho, B.-H. Kim, and S.-J. Park, Appl. Phys. Lett. **89**, 013116 (2006).

<sup>19</sup>S. Huang, S. Banerjee, R. T. Tung, and S. Oda, J. Appl. Phys. **93**(1), 576