# Virginia Commonwealth University **VCU Scholars Compass**

Theses and Dissertations

Graduate School

2018

# IMPROVING THE PERFORMANCE AND ENERGY EFFICIENCY OF **EMERGING MEMORY SYSTEMS**

Yuhua Guo Virginia Commonwealth University

Follow this and additional works at: https://scholarscompass.vcu.edu/etd

Part of the Computer and Systems Architecture Commons, and the Data Storage Systems Commons

© The Author

#### Downloaded from

https://scholarscompass.vcu.edu/etd/5317

This Dissertation is brought to you for free and open access by the Graduate School at VCU Scholars Compass. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of VCU Scholars Compass. For more information, please contact libcompass@vcu.edu.

©Yuhua Guo, May 2018 All Rights Reserved.

# IMPROVING THE PERFORMANCE AND ENERGY EFFICIENCY OF EMERGING MEMORY SYSTEMS

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy at Virginia Commonwealth University.

by

# YUHUA GUO

M.S., Huazhong Univ. of Sci. and Tech. - Sep. 2008 to Apr. 2011 B.S., Shaanxi Univ. of Sci. and Tech. - Sep. 2003 to Jul. 2007

Advisor: Weijun Xiao, Ph.D.,

Assistant Professor, Department of Electrical and Computer Engineering

Virginia Commonwealth University

Co-advisor: Xubin He, Ph.D.,

Professor, Department of Computer and Information Sciences

Temple University

Virginia Commonwealth University Richmond, Virginia May, 2018

## Acknowledgements

I would like to thank my advisor Dr. Weijun Xiao and co-advisor Dr. Xubin He, for their training and guidance on my Ph.D. study and research. I give my special thanks to Dr. He, for his patience and advice on my research, encouraging me to attend academic conferences, introducing intern opportunity for me, and his generous support to help me finish my Ph.D. program. I would like to express my gratitude to Dr. Qing Liu as my mentor at Oak Ridge National Laboratory. He helped to polish my first paper and made it accepted.

I would like to thank my committee members, Dr. Preetam Ghosh, Dr. Carl Elks, and Dr. Wei Cheng, for serving on my advisory committee and for their insightful comments. I would also like to extend my thanks to other faculty and stuff members of the department of Electrical and Computer Engineering, in particularly to the administrative assistants Stacy E. Metz and Ellen Gresham. Meanwhile, I thank my STAR Lab mates, Tao Lu, Kun Tang, Ping Huang, Pradeep Subedi, and other lab mates Qianbin Xia, Dongwei Wang, Liang Xu. They helped me a lot and we spent a good time together. I thank my friends, Bob and Elaine Metcalf, Jim and Jan Fiorelli, Dick and Janet Andrews, Lex and Kate Strickland, Bud Whitehouse, Ed and Suping Boudreau, Geoffrey and Eunice Chan, for our friendships at Richmond.

I cannot express my gratitude to my wife, Qiong. Without her unfailing support and love, it is impossible to complete this dissertation. I thank my little son Leo for bring joy to the family. His joy is precious to me. I thank my parents, parents in law and my brother for their love, encouraging and support.

# TABLE OF CONTENTS

| Chapter                                             | Pag      |

|-----------------------------------------------------|----------|

| Acknowledgements                                    | <br>. j  |

| Table of Contents                                   | <br>. ii |

| List of Tables                                      |          |

| List of Figures                                     | <br>. v  |

| Abstract                                            |          |

| 1 Introduction                                      |          |

| 1.1 Background and Problem Statement                |          |

| 2 Alleviating DRAM Refresh Overhead                 |          |

| 2.1 Introduction                                    |          |

| 2.2 Background and Motivation                       |          |

| 2.2.1 DRAM Refresh                                  |          |

| 2.2.2 Refresh Penalty                               |          |

| 2.2.3 Limitations of Existing Solutions             |          |

| 2.3 Architecture and Design                         |          |

| 2.3.1 DRAM Refresh Characterization                 |          |

| 2.3.2 The RPC Architecture                          |          |

| 2.3.3 Cache Design                                  |          |

| 2.3.4 Implementation Overhead                       |          |

| 2.4 Evaluation                                      |          |

| 2.4.1 Evaluation Methodology                        |          |

| 2.4.2 Design Space Exploration                      |          |

| 2.4.4 Four-Core Simulation Results                  |          |

| 2.5 Related Work                                    |          |

| 3 Architecting Die-stacked DRAM as A Part of Memory | <br>. 3  |

| 3.1 Introduction                                    | <br>. 3  |

|   | 3.2  | Background and Motivation                               |

|---|------|---------------------------------------------------------|

|   |      | 3.2.1 OS-managed PoM                                    |

|   |      | 3.2.2 Hardware-managed PoM                              |

|   |      | 3.2.2.1 Line-based PoM                                  |

|   |      | 3.2.2.2 Page-based PoM                                  |

|   | 3.3  | Architecture and Design                                 |

|   |      | 3.3.1 Remapping Table Design                            |

|   |      | 3.3.2 Page Swapping                                     |

|   |      | 3.3.3 Page Footprints                                   |

|   |      | 3.3.4 Line Location Prediction                          |

|   |      | 3.3.5 Put Everything Together                           |

|   |      | 3.3.6 Overhead Comparison                               |

|   | 3.4  | Evaluation                                              |

|   |      | 3.4.1 Evaluation Methodology                            |

|   |      | 3.4.2 Performance Results                               |

|   |      | 3.4.3 Hit Ratio and Off-chip Traffic                    |

|   |      | 3.4.4 Prediction Accuracy                               |

|   |      | 3.4.5 Energy Analysis                                   |

|   |      | 3.4.6 Sensitivity to RPT Cache Size                     |

|   |      | 3.4.7 Sensitivity to Swap Threshold                     |

|   | 3.5  | Related Work                                            |

| 4 | D    | DI CONTRACTOR DI LA |

| 4 | Page | Placement in Die-stacked DRAM/NVM Memory Systems        |

|   | 4.1  | Introduction                                            |

|   | 4.2  | Background and Motivation                               |

|   |      | 4.2.1 Emerging Memory Technologies                      |

|   |      | 4.2.2 Hybrid Memory Systems                             |

|   | 4.3  | Architecture and Design                                 |

|   |      | 4.3.1 HBM Cache Design                                  |

|   |      | 4.3.2 HBM Cache Bypassing                               |

|   |      | 4.3.3 Page Migration                                    |

|   |      | 4.3.4 Write Reduction                                   |

|   | 4.4  | Evaluation                                              |

|   |      | 4.4.1 Evaluation Methodology                            |

|   |      | 4.4.2 Performance Results                               |

|   |      | 4.4.3 Write Traffic on PCM                              |

|   |      | 4.4.4 Energy Consumption                                |

|   |      | 4.4.5 Overhead Analysis                                 |

|   |      |                                                         |

| 4.4.6 Sensitivity Study                        |     |  |  |   |   | 80 |

|------------------------------------------------|-----|--|--|---|---|----|

| 4.4.6.1 Migration Threshold Sensitivity Analys | sis |  |  |   |   | 80 |

| 4.4.6.2 HBM Cache Size Sensitivity Analysis    |     |  |  |   |   | 80 |

| 4.5 Related Work                               |     |  |  |   |   | 82 |

| 5 Conclusions and Future Work                  |     |  |  |   |   | 84 |

| 5.1 Conclusions                                |     |  |  |   |   |    |

| 5.2 Future Work                                |     |  |  |   |   | 85 |

| References                                     |     |  |  |   |   | 87 |

| Vita                                           |     |  |  | _ | _ | 99 |

# LIST OF TABLES

| Tab | ole                                                                              | Page |

|-----|----------------------------------------------------------------------------------|------|

| 1   | Refresh related parameters under different DRAM densities                        | 10   |

| 2   | tREFI and tRFC parameters in different refresh modes with various DRAM densities | 13   |

| 3   | Notations used in Equation 2.1                                                   | 19   |

| 4   | Configuration of Simulators                                                      | 22   |

| 5   | Storage Overhead Comparison                                                      | 46   |

| 6   | System Configuration                                                             | 47   |

| 7   | The breakdown of prediction accuracy                                             | 52   |

| 8   | Workload Statistics                                                              | 68   |

| 9   | Page Eviction Cases in HBM Cache                                                 | 72   |

| 10  | System Parameters                                                                | 73   |

| 11  | Storage Overhead Comparison                                                      | 80   |

# LIST OF FIGURES

| Fig | ure                                                                                                                                                                                                                                                                                                                                | Page  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

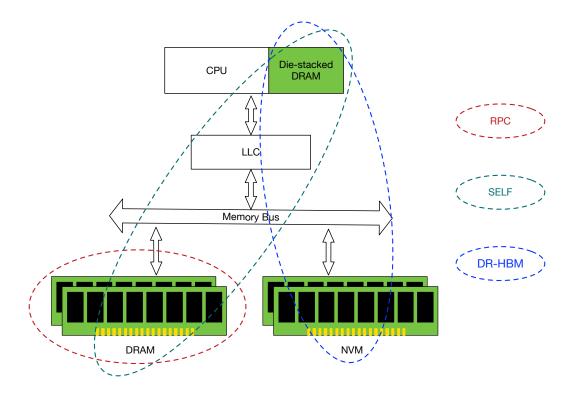

| 1   | The architecture of modern memory systems. The proposed approaches address problems in different memory technologies, which are circled with dotted lines                                                                                                                                                                          | 4     |

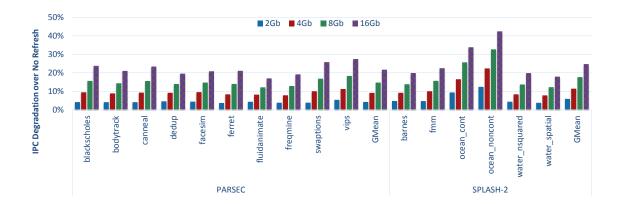

| 2   | Performance degradation with various chip capacities in the normal temperature range ( $\leq 85^{\circ}$ C). The geometric mean values are 21.7% and 24.7% for the PARSEC and SPLASH-2 benchmark suites, respectively                                                                                                              | y. 11 |

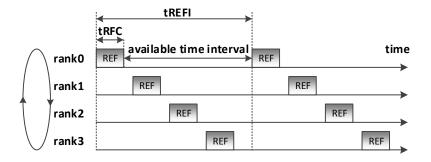

| 3   | Staggered refresh in ranks within the same channel                                                                                                                                                                                                                                                                                 | 15    |

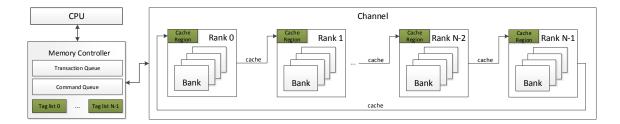

| 4   | The RPC architecture. The to-be-read data is cached in an adjacent rank before the target rank is locked and each rank reserves or over-provisions a cache region to store the cached data. All cache regions are organized in a rotated fashion                                                                                   | 16    |

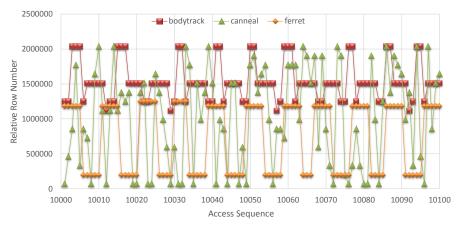

| 5   | Access locality of PARSEC benchmark suite running on two-rank DRAM system. X-axis represents access sequence and Y-axis is the row number calculated by Equation 2.1. 100 consecutive memory accesses are randomly chosen to show                                                                                                  | 18    |

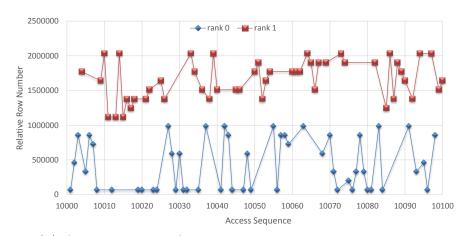

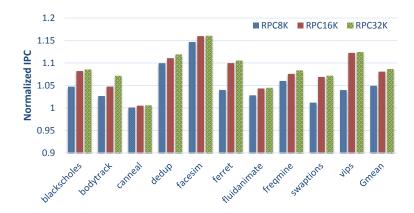

| 6   | The performance of $RPC$ with various cache size, normalized to the 1x mode refresh scheme                                                                                                                                                                                                                                         | 24    |

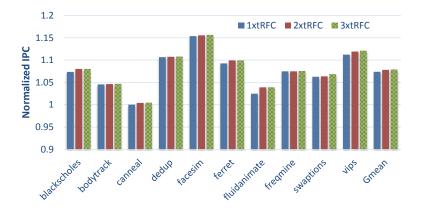

| 7   | The performance of $RPC$ with various $tCI$ , normalized to the 1x mode refresh scheme                                                                                                                                                                                                                                             | 24    |

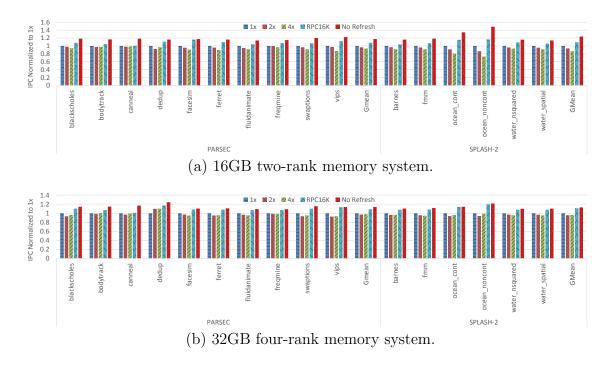

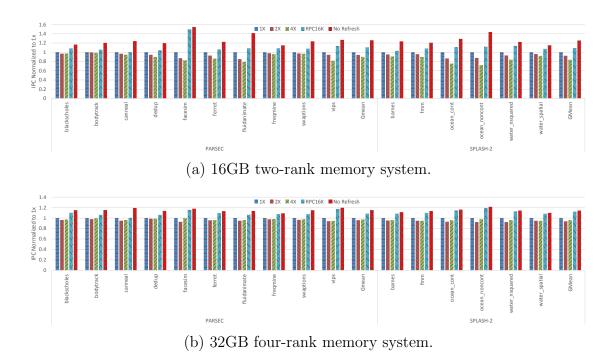

| 8   | Performance comparisons among $FGR$ , $RPC$ and $No\ Refresh$ schemes with various number of ranks in a single-core system. $RPC$ outperforms all $FGR$ modes and improves system performance by 8.1% (8.7%) and 9.6% (10.8%) on average for PARSEC and SPLASH-2 benchmark suites in the two-rank (four-rank) system, respectively | 25    |

| 9  | Performance comparisons among FGR, RPC and No Refresh schemes with various number of ranks in a four-core system. RPC outperforms all FGR modes and improves system performance by 10.7% (8.6%) and 9.3% (12.2%) on average for PARSEC and SPLASH-2 benchmark suites in the two-rank (four-rank) system, respectively                                                  | 27 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

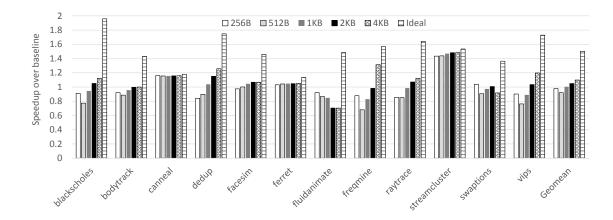

| 10 | The performance of a state-of-the-art page-based PoM design [47] with different page sizes. All requests are serviced from on-chip memory in the ideal case. On average, the page-based design performs best at the page size of 4KB                                                                                                                                   | 36 |

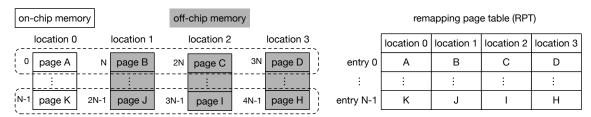

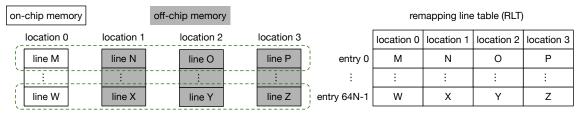

| 11 | Direct remapping and corresponding remapping tables                                                                                                                                                                                                                                                                                                                    | 38 |

| 12 | The data layout of on-chip memory after co-locating each data line with its corresponding RLT entry                                                                                                                                                                                                                                                                    | 40 |

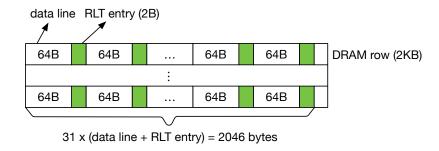

| 13 | Overview of SELF architecture. When the competing counter (CC) is larger than the swap threshold, SELF selectively swaps lines in the requested page according to its page footprint. Otherwise, SELF uses page location to predict the requested line location to reduce latency of off-chip accesses                                                                 | 44 |

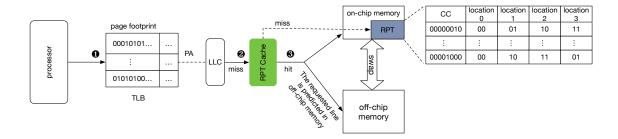

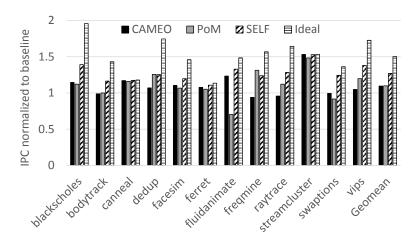

| 14 | Performance comparisons. On average, CAMEO and PoM improve performance by 9.5% and 9.9%, respectively, while SELF improves performance by 26.9%, which is 85% of the ideal case                                                                                                                                                                                        | 48 |

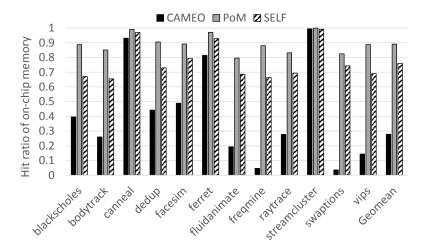

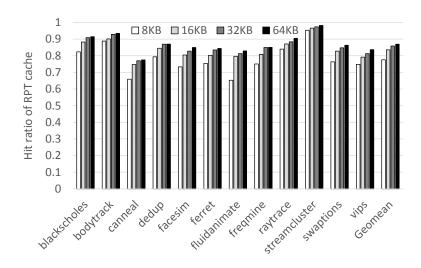

| 15 | Two import performance metrics (a) hit ratio of on-chip memory and (b) off-chip traffic. All results are normalized to the baseline. SELF achieves an average hit ratio of 76% while reducing off-chip traffic to 46% of the baseline system. Although PoM obtains the highest hit ratio, 89% on average, it also causes the highest off-chip traffic, 153% on average | 50 |

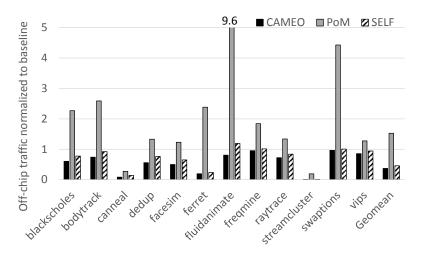

| 16 | Energy consumption. On average, CAMEO, PoM and SELF reduce energy per access by 31.3%, 27.6% and 47.9%, respectively                                                                                                                                                                                                                                                   | 53 |

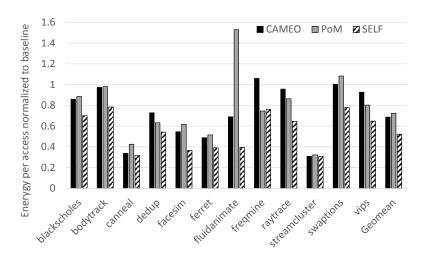

| 17 | Hit ratio of RPT cache across different cache size                                                                                                                                                                                                                                                                                                                     | 54 |

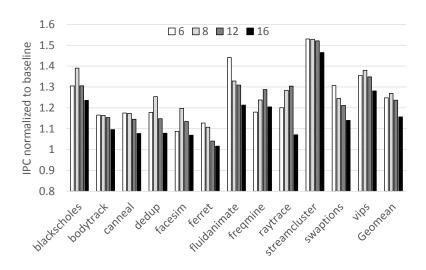

| 18 | Performance sensitivity to various swap thresholds (6, 8, 12, and 16)                                                                                                                                                                                                                                                                                                  | 55 |

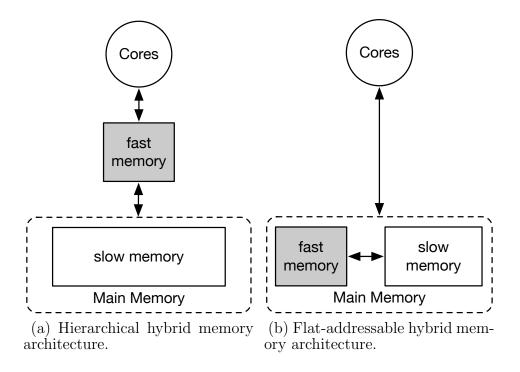

| 19 | Typical hybrid memory system architectures                                                                                                                                    | 63 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

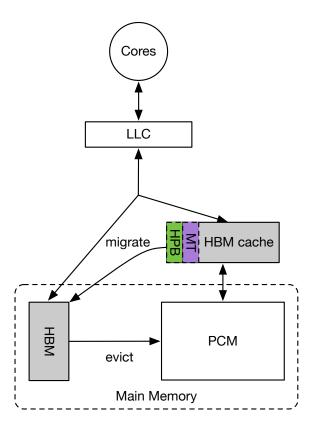

| 20 | The architecture of DR-HBM. The miss table (MT) and hot page buffer (HPB) are reserved in HBM cache                                                                           | 66 |

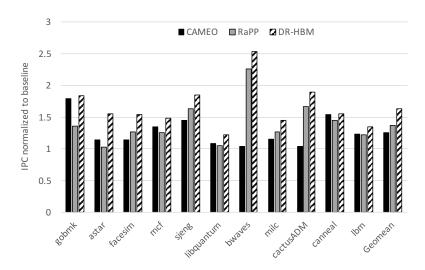

| 21 | Performance comparisons. On average, CAMEO and RaPP improve performance by 25% and 37.1%, respectively, as compared to the baseline, while DR-HBM improves performance by 63% | 74 |

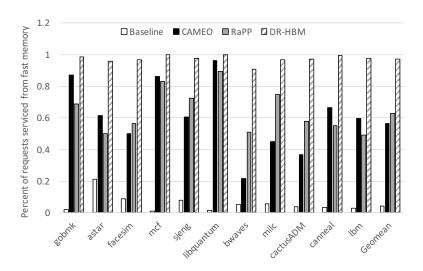

| 22 | Hit ratio of fast memory. Baseline, CAMEO, RaPP and DR-HBM achieve an average hit ratio of 4.2%, 56.6%, 63%, and 97.2%, respectively.                                         | 75 |

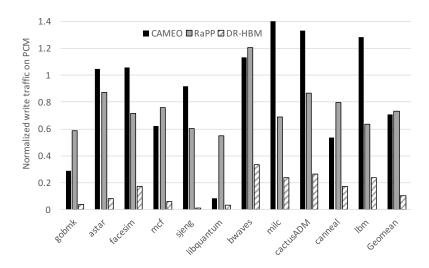

| 23 | The write traffic on PCM. Compared to the baseline, CAMEO, RaPP and DR-HBM reduce the write traffic on PCM by 29.4%, 26.6% and 89.6% on average, respectively                 | 77 |

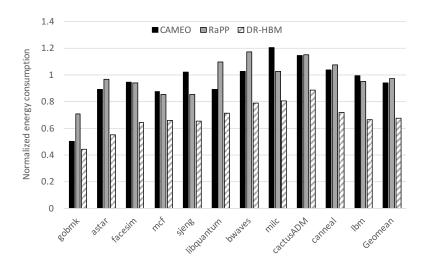

| 24 | Energy consumption. Compared to the baseline, CAMEO, RaPP and DR-HBM reduce the energy consumption by 6.3%, 3% and 32.9% on average, respectively                             | 78 |

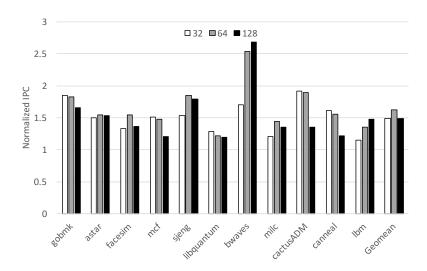

| 25 | Performance sensitivity to the migration threshold (32, 64, and 128)                                                                                                          | 81 |

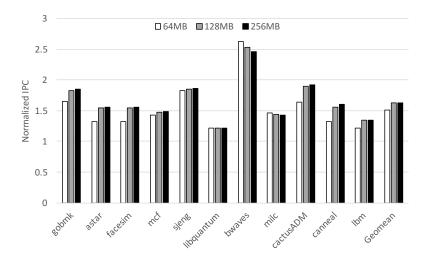

| 26 | Performance sensitivity to the HBM cache size (64MB, 128MB, and 256MB).                                                                                                       | 81 |

#### Abstract

# IMPROVING THE PERFORMANCE AND ENERGY EFFICIENCY OF EMERGING MEMORY SYSTEMS

# By Yuhua Guo

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy at Virginia Commonwealth University.

Virginia Commonwealth University, 2018.

Advisor: Weijun Xiao, Ph.D.

Assistant Professor, Virginia Commonwealth University

Co-advisor: Xubin He, Ph.D.

Professor, Temple University

Modern main memory is primarily built using dynamic random access memory (DRAM) chips. As DRAM chip scales to higher density, there are mainly three problems that impede DRAM scalability and performance improvement. First, DRAM refresh overhead grows from negligible to severe, which limits DRAM scalability and causes performance degradation. Second, although memory capacity has increased dramatically in past decade, memory bandwidth has not kept pace with CPU performance scaling, which has led to the memory wall problem. Third, DRAM dissipates considerable power and has been reported to account for as much as 40% of the total system energy and this problem exacerbates as DRAM scales up.

To address these problems, 1) we propose Rank-level Piggyback Caching (RPC) to alleviate DRAM refresh overhead by servicing memory requests and refresh operations in parallel; 2) we propose a high performance and bandwidth efficient approach, called

SELF, to breaking the memory bandwidth wall by exploiting die-stacked DRAM as a part of memory; 3) we propose a cost-effective and energy-efficient architecture for hybrid memory systems composed of high bandwidth memory (HBM) and phase change memory (PCM), called Dual Role HBM (DR-HBM). In DR-HBM, hot pages are tracked at a cost-effective way and migrated to the HBM to improve performance, while cold pages are stored at the PCM to save energy.

# CHAPTER 1

#### INTRODUCTION

## 1.1 Background and Problem Statement

The capacity of main memory keeps increasing, which is mainly driven by the growing memory requirements of new applications, and the increasing number of processing cores in a single chip. Dynamic Random Access Memory (DRAM) has been used as the main memory in computer systems for decades. However, DRAM-based memory systems are mainly facing three scalability problems.

First, DRAM cells leak charge over time, causing stored data to be lost. Therefore, periodic refreshes are required to ensure data integrity. Commodity DRAM refreshes cells at rank level, resulting in an entire rank being unavailable during a refresh period. As DRAM density keeps increasing, more rows need to be refreshed during a single refresh operation, which causes higher refresh latency and significantly degrades the overall memory system performance [1]. Currently refresh overhead has become the biggest restriction for DRAM scalability, making it increasingly important to reduce refresh overhead [2].

Second, although memory capacity has increased dramatically in past decade, memory bandwidth has not kept pace with CPU performance scaling, which has led to the memory wall problem [3]. Die-stacked DRAM (a.k.a., on-chip DRAM) provides much higher bandwidth and lower latency than off-chip DRAM. It is a promising technology to break the "memory wall". However, on-chip DRAM is not large enough to fully replace off-chip DRAM. Therefore, on-chip DRAM is used either as a cache (i.e., DRAM cache) or as a part of memory (PoM). A DRAM cache design would suffer

from more page faults than a PoM design as the DRAM cache cannot contribute towards capacity of main memory. In the meanwhile, obtaining high performance requires PoM systems to swap requested data to the on-chip DRAM. Existing PoM designs fall into two categories — line-based and page-based. The former ensures low off-chip bandwidth utilization but suffers from a low hit ratio of on-chip memory due to limited temporal locality. In contrast, page-based designs achieve a high hit ratio of on-chip memory while at the cost of moving large amounts of data between on-chip and off-chip memories, leading to increased off-chip bandwidth utilization and significant system performance degradation. How to achieve a similar high hit ratio of on-chip memory as page-based designs and eliminate excessive off-chip traffic involved is a big challenge.

Last, traditional DRAM-based memory systems are also facing the power issue besides the memory wall problem. DRAM dissipates considerable power and has been reported to account for as much as 40% of the total system energy [4, 5, 6]. This problem exacerbates as DRAM capacity increases. Therefore, emerging non-volatile memories (NVMs), such as Spin-Transfer Torque RAM (STT-RAM) and Phase Change Memory (PCM), are gaining interest as DRAM alternatives as they have near-zero standby power. However, NVMs have lower memory bandwidth and longer access latency than DRAM, aggravating the memory wall problem. Since die-stacked DRAM has the potential to break the memory wall but its capacity is insufficient to fully replace DRAM memory, a die-stacked DRAM/NVM hybrid memory system could be a promising way to build a high performance, large capacity, and energy efficient memory system. In order to fully exploit high performance (i.e. high bandwidth and low latency) offered by die-stacked DRAM and large capacity offered by NVM, hot pages should be migrated to die-stacked DRAM to improve performance and cold pages should be stored in NVM to save energy. Therefore, how to identify hot pages

is very critical. Prior work regarding DRAM/NVM hybrid memory systems [7, 8, 9, 10] has been proposed. However, the ways used to track page hotness in prior work are costly due to redesigning the memory controller (MC) or extending translation lookaside buffer (TLB). Moreover, the hot page stays at NVM until its access count exceeds the migration threshold, which could miss lots of opportunities to improve performance. Therefore, it is very promising to design a cost-effective and energy efficient architecture for die-stacked DRAM/NVM memory systems.

## 1.2 Proposed Approaches

Figure 1 shows the architecture of modern memory systems, which could consist of traditional DRAM, die-stacked DRAM and emerging NVMs. As stated in Section 1.1, each component has its own limitations. In order to build a high performance, large capacity, and energy efficient memory system, we propose three approaches to address these three scalability problems, respectively, as shown in Figure 1.

First, to mitigate DRAM refresh overhead, we propose a caching scheme, called Rank-level Piggyback Caching, or RPC for short, based on the fact that ranks in the same channel are refreshed in a staggered manner. The key idea is to cache the to-be-read data in a rank (e.g. Rank 1) to its adjacent rank (e.g. Rank 2) before Rank 1 is locked for refresh. Each rank reserves or over-provisions a very small area, denoted as a cache region, to store the cached data. The cache regions from all ranks are organized in a rotated fashion. In other words, the cached data for the last rank is stored in the first rank. When a read request arrives at a rank undergoing refresh, the memory controller first checks the cache region in the next rank in the same channel; if the requested data is cached, the memory controller services the request from the cache without waiting for the refresh operation to complete, which reduces memory access latency and improves system performance.

Fig. 1. The architecture of modern memory systems. The proposed approaches address problems in different memory technologies, which are circled with dotted lines.

Second, to achieve a similar high hit ratio of on-chip memory as page-based designs, and eliminate excessive off-chip traffic involved, we propose SELF, a high performance and bandwidth efficient approach. The key idea is to <u>SE</u>lectively swap <u>Lines</u> in a requested page that are likely to be accessed according to page <u>F</u>ootprint, instead of blindly swapping an entire page. In doing so, SELF allows incoming requests to be serviced from the on-chip memory as much as possible, while avoiding swapping unused lines to reduce memory bandwidth consumption.

Last, we propose a cost-effective and energy-efficient architecture for die-stacked

DRAM/NVM memory systems, especially for HBM/PCM memory systems, called Dual Role HBM (DR-HBM). In DR-HBM, the HBM plays two roles and is divided into two parts. A small portion of which, called HBM cache, is used as a cache for the PCM. The remaining HBM is used as a part of main memory. Furthermore, the HBM cache is also used to track page hotness without additional hardware support. In order to improve performance and reduce writes to the PCM, we propose three techniques. First, CSM (cache on the second miss) increases the effectiveness of HBM cache and reduces PCM traffic by avoiding to cache singleton pages which contain only single useful data blocks; Second, hot pages are migrated in batches to amortize TLB shoot-down overhead; Third, we propose Hot First LRU (HF-LRU) page replacement policy and increase the weight of write operations to reduce writes to the PCM.

# CHAPTER 2

#### ALLEVIATING DRAM REFRESH OVERHEAD

#### 2.1 Introduction

Modern main memory is primarily built using dynamic random access memory (DRAM) cells. A DRAM cell consists of one access transistor and one capacitor. Each DRAM cell stores one bit of data as electrical charge in the capacitor; over time charge will leak from the capacitor and can cause data loss. Therefore, DRAM requires an operation called *refresh* that periodically restores electrical charge in capacitors to ensure data integrity.

Each DRAM cell is refreshed every 64ms (or 32ms above 85 °C) as specified by the JEDEC standards [11]. This time period is called retention time. All DRAM rows are refreshed within this time period. The total time spent on refresh operations is proportional to the number of rows in a DRAM device (a.k.a. a chip). Initially all DRAM rows are refreshed sequentially within one refresh operation, which causes long periods of memory unavailability. To avoid this long latency, all DRAM rows in a bank are divided into 8K groups, and each group is refreshed within a time period of  $64\text{ms}/8\text{K} = 7.8\mu\text{sec}$  ( $3.9\mu\text{sec}$  at high temperatures). This time duration is called refresh interval, denoted as tREFI. The memory controller sends a refresh command to DRAM devices once every tREFI. The time duration of one refresh command is referred to as refresh cycle, denoted as tRFC. Each DRAM row is composed of thousands of bits. The size of each row is referred to as page size, and the capacity of a DRAM device is the number of rows in a device times the page size. The page size has remained between 1KB to 2KB for several DRAM generations while the number

of rows per device has scaled linearly with DRAM device capacity. As the capacity of the DRAM device increases and the refresh interval remains unchanged, the refresh cycle increases quickly since more DRAM rows need to be refreshed in each refresh operation. As a result, it takes a longer time and more energy to complete a refresh.

The observation that motivates this work is that commodity DRAM refreshes cells at rank level. As a result, an entire rank is locked up and cannot serve any pending memory request while being refreshed. Thus, a read request arriving at a rank that is being refreshed is forced to wait until the refresh operation is completed, which would increase read latency and degrades system performance. As memory technology scales to higher densities, for example, 16Gb DRAM device that has been defined in DDR4 SDRAM standard [12], performance degradation and energy consumption that attributes to refresh grow from negligible to severe. Currently refresh overhead has become the biggest restriction for DRAM scalability, making it increasingly important to reduce refresh overhead [2].

Our goal is to alleviate the performance degradation due to DRAM refresh operations. As ranks within a channel are refreshed in a staggered fashion, while one rank is being refreshed, the remaining ranks can still service memory requests. In light of this, we propose RPC (Rank-level Piggyback Caching) [13], a scheme that allows concurrent refresh and memory access in a DRAM system. The basic idea is to cache the data that will be likely accessed during the next refresh period to an adjacent rank in the same channel before the target rank is locked. As such, read requests issued to a rank which is being refreshed can be served from another rank without waiting for the refresh to complete. Without being blocked during refresh, the read latency can be significantly shortened and system performance in terms of instructions per cycle can be improved.

# 2.2 Background and Motivation

A modern DRAM-based memory system has one or more memory controllers, each of which manages one or more channels. Each channel has independent command, address, and data buses, allowing different channels to be accessed concurrently. Each channel is composed of a number of ranks that share the channel bandwidth and operate simultaneously to service memory requests. Each rank can further divided into DRAM chips and within each chip, there are a number of banks (typically 8 banks) which can be accessed in parallel as well. Each bank consists of a two-dimensional array of DRAM cells. A DRAM cell consists of one access transistor and one capacitor. Each DRAM cell can store one bit of data as electrical charge in the capacitor. All the access transistors in the same column connect their capacitors to a wire called bitline. An access transistor is controlled by a wire called wordline which is shared by a row of DRAM cells. DRAM cells sharing a wordline form a DRAM row. Each bitline connects to a sense amplifier, a row of which is known as row buffer which is used to sense and amplify the voltage of each bitline [14]. A bank can be further sub-divided into many subarrays, with each having its own row buffer (a.k.a. local row buffer). However, only one subarray can be accessed at a time since all subarrays share the global bitlines. All subarrays' row buffers are connected to a global I/O buffer. The memory controller reads/writes data from/to the I/O buffer through the bank's I/O bus.

A bank supports four types of operations: activation (ACT or RAS), read/write (CAS), precharge (PRE) and refresh (REF). To retrieve data from DRAM cells, the row which contains the requested data must first be activated (or opened) to put the entire row's content into the row buffer through bitlines. Then the requested data can be retrieved from the row buffer by decoding the column address. If subsequent

requests access the same row in the same bank, a row hit happens, otherwise a row miss occurs. There are two row buffer management policies: open page and close page [15]. In the open page mode, the accessed row is not closed until a different row within the same bank is accessed. The activation operation can be obviated if it is a row hit. Otherwise the memory controller first needs to close the row and precharges bitlines for the next activation, which causes extra latency and power consumption [16]. Therefore, the open page mode is more suitable for workloads with good access locality. In contrast, in the close page mode, the memory controller proactively closes the row and precharges bitlines as soon as an access is over, which provides a consistently fair latency. It is clear that the close page mode is beneficial for workloads with poor access locality, such as, the multi-core environments where there could be mutual interferences from different applications.

# 2.2.1 DRAM Refresh

Due to capacitor current leakage, each DRAM cell needs to be refreshed periodically to maintain data integrity. DRAM cells are refreshed in the unit of a row. A refresh operation consists of two steps. First, data in the refreshing row is read out and written back to the cells to restore each capacitor's charge, which is actually the activation operation. Then the bitlines are precharged for the next refresh operation. Hence, the refresh operation is functionally equivalent to an activation plus a precharge operation. The time taken to refresh one row is known as row cycle time (tRC), which is the time used to activate and precharge one row. DRAM cells have varying retention time [17] and the JEDEC standards specify a minimum of 64ms (or 32ms at high temperatures), which means all DRAM rows must be refreshed within this time period. Initially, there were relatively few rows in a bank, therefore it was viable to refresh all DRAM rows in succession within retention time. This is referred

to as bursty refresh mode. However, refreshing all DRAM rows in bulk incurs high latency, which becomes unacceptable as the number of DRAM rows in a bank increases to tens of thousands. To avoid this high latency, JEDEC supports distributed refresh mode, in which DRAM rows in a bank are divided into 8K groups. The memory controller issues a refresh command to refresh one group every tREFI which is equal to  $64 \text{ms/8k} = 7.8 \mu \text{sec}$  (3.9  $\mu \text{sec}$  at high temperatures). The time spent on refreshing one group is known as refresh cycle or tRFC, which is a function of tRC. The tREFI has remained unchanged for several generations, but tRFC increases linearly as DRAM chip scales to higher densities. tRFC/tREFI is defined as refresh duty cycle (RDC) [18], the percentage of time that the DRAM system spends on doing refresh. Table 1 shows several refresh related parameters under different chip densities. Values for 16Gb chip are extrapolated. The number of rows (Row Num.) in a bank doubles as the density of DRAM chip is doubled, as does the number of rows refreshed in each refresh operation (Rows/REF) because the total number of refresh operations (Refresh Num.) in the retention time period remains constant. Therefore, the tRFC increases linearly as DRAM density increases, as does the RDC.

Table 1. Refresh related parameters under different DRAM densities.

| Chip Density                    | 1Gb [19] | 2Gb [20] | 4Gb [21] | 8Gb [22] | 16Gb    |

|---------------------------------|----------|----------|----------|----------|---------|

| Retention Time(ms)              | 64/32    | 64/32    | 64/32    | 64/32    | 64/32   |

| Row Num.                        | 16K      | 32K      | 64K      | 128K     | 256K    |

| Refresh Num.                    | 8K       | 8K       | 8K       | 8K       | 8K      |

| Rows/REF                        | 2        | 4        | 8        | 16       | 32      |

| $\mathrm{tREFI}(\mu\mathrm{s})$ | 7.8/3.9  | 7.8/3.9  | 7.8/3.9  | 7.8/3.9  | 7.8/3.9 |

| tRC(ns)                         | 51       | 51       | 51       | 51       | 51      |

| tRFC(ns)                        | 110      | 160      | 260      | 350      | 450     |

| $\mathrm{tRFC}/\mathrm{tREFI}$  | 1.41%    | 2.05%    | 3.34%    | 4.34%    | 5.77%   |

| $tRFC/tREFI (> 85 ^{\circ}C)$   | 2.82%    | 4.11%    | 6.68%    | 8.68%    | 11.54%  |

Fig. 2. Performance degradation with various chip capacities in the normal temperature range (≤ 85 °C). The geometric mean values are 21.7% and 24.7% for the PARSEC and SPLASH-2 benchmark suites, respectively.

# 2.2.2 Refresh Penalty

In theory, a refresh scheme at any granularity is valid as long as all cells can be refreshed timely. However, commodity DRAM refreshes cells at rank level, which means all chips in a rank and all banks in a chip are refreshed in a lockstep manner. A rank which is undergoing a refresh cannot serve any memory access. In other words, refresh and memory access are mutually exclusive to each other at the granularity of a rank, which is the main contributing factor of refresh penalty [23].

As shown in Table 1, the tRFC is growing dramatically with chip density increases, which aggravates the refresh penalty. The RDC increases to 11.54% when DRAM chip capacity increases to 16Gb, which means a rank spends 11.54% of the time refreshing. Therefore, the refresh overhead is no longer trivial and will degrade system performance significantly. Figure 2 shows the performance degradation due to refresh compared to an ideal case without refresh. When DRAM chips scale to 16Gb, the performance degradation can be as high as 42.4% for memory latency sensitive workloads and the geometric mean values are 21.7% and 24.7% for the PARSEC and

SPLASH-2 benchmark suites, respectively. The performance degradation becomes more severe as DRAM chip density increases, demonstrating that it is increasingly important to alleviate refresh overhead in high density memory.

# 2.2.3 Limitations of Existing Solutions

JEDEC specifications define the refresh scheduling flexibility: up to eight refresh commands can be postponed or issued in advance. Stuecheli et al. [1] proposed Elastic Refresh (ER), which leverages the 8-tREFI refresh scheduling flexibility to hide refresh penalty. ER prioritizes DRAM accesses over DRAM refresh operations by postponing refresh operations to decrease the probability of conflicts between them. Every refresh command needs to wait an elastic window period determined by the average idle time of the rank and the number of already postponed refresh commands to avoid interfering with demand requests. In fact, previous work DUE [24] makes use of the flexibility in issuing refresh operations by scheduling them when the rank queues are idle. ER further defers refresh operations for an extra time period after the rank becomes idle to service the incoming requests with priority, but the postponed refresh commands need to be enforced immediately when the number of postponed refresh commands hits the 9-tREFI limitation. However, ER becomes less effective as DRAM scales [23], [25]. The increasing tRFC makes the refresh latency hard to be hidden as the average rank idle period is shorter than tRFC. Moreover, ER incurs extra delay when it incorrectly predicts a time period as idle when it actually has pending requests.

A read request arriving at a rank which is undergoing a refresh operation needs to wait until the refresh operation completes. In the worst case scenario it must wait for tRFC. To shorten the tRFC, Fine Granularity Refresh (FGR) was proposed in the DDR4 SDRAM Standard [12]. FGR defines three refresh modes with different refresh

rates (i.e. tREFI). They are 1x mode, 2x mode and 4x mode respectively, and the memory controller can switch between them on the fly. The 1x mode is the same as the traditional refresh scheme defined in [11], in which each refresh command is issued every tREFI<sub>1x</sub> =  $7.8\mu$ sec. The 2x and 4x modes require that refresh commands are issued two and four times as frequently as 1x mode. Due to the increasing number of refresh commands, fewer rows need to be refreshed during a single refresh. Therefore, the tRFC is reduced accordingly in the 2x and 4x modes. Table 2 shows that the tREFI and tREC parameters under different refresh modes vary with different DRAM densities. Values for 16Gb DRAM chips which are not decided in the DDR4 standard [12], are extrapolated based on the previous values of low densities; we use the 8Gb chip as the default DRAM chip in our experiments. The refresh cycle is reduced as the refresh rate increases. We implement FGR in DRAMSim2 [26] and run different benchmarks in PARSEC 2.1 [27] and SPLASH-2 [28] benchmark suites to observe the performance of FGR.

Table 2. tREFI and tRFC parameters in different refresh modes with various DRAM densities.

| Refresh Mode | Parameter            | 2Gb        | 4Gb        | 8Gb        | 16Gb       |

|--------------|----------------------|------------|------------|------------|------------|

| 1x mode      | $tREFI_{1x} (\mu s)$ | 7.8/3.9    | 7.8/3.9    | 7.8/3.9    | 7.8/3.9    |

| 1x mode      | $tRFC_{1x}$ (ns)     | 160        | 260        | 350        | 450        |

| 2x mode      | $tREFI_{2x} (\mu s)$ | 3.9/1.95   | 3.9/1.95   | 3.9/1.95   | 3.9/1.95   |

| 2X mode      | $tRFC_{2x}$ (ns)     | 110        | 160        | 260        | 350        |

| 4x mode      | $tREFI_{4x} (\mu s)$ | 1.95/0.975 | 1.95/0.975 | 1.95/0.975 | 1.95/0.975 |

| 47 mode      | $tRFC_{4x}$ (ns)     | 90         | 110        | 160        | 260        |

Figure 8 shows the performance (IPC) of FGR in the two-rank and four-rank systems. All results are normalized to the 1x mode. In the two-rank DRAM system, the performance of both 2x and 4x modes are worse than 1x mode. There are two reasons: 1) tRFC reduces linearly but not proportionally as the refresh rate in-

creases, which means  $2xtRFC_{2x}$  is larger than  $1xtRFC_{1x}$ , and  $2xtRFC_{4x}$  is larger than  $1xtRFC_{2x}$  too; 2) Both PARSEC and SPLASH-2 benchmark suites are composed of multi-thread and memory-sharing programs, which are memory-intensive workloads (detailed analysis can be found in Section 2.4.3). In the memory-intensive case, the average rank idle period is even shorter than  $tRFC_{4x}$ , so the refresh penalty cannot be hidden. Thus an application only needs to wait for one  $tRFC_{1x}$  in the 1x mode, it may experience 2 (or 4) stalls in the 2x (or 4x) mode because of the increasing refresh rate. The total time spent on doing refresh is longer than that in 1x mode, which causes performance degradation in the 2x mode and 4x mode. In the four-rank system, the average performance of 2x and 4x modes are better than that in the two-rank system, respectively. For dedup benchmark, both 2x and 4x modes even perform better than 1x mode. The reason is that the increasing number of ranks reduces the probability of conflicts between memory requests and DRAM refreshes, thereby the DRAM system can get benefit from the reduced tRFC. Overall, FGR is not suitable for memory-intensive workloads.

All refresh schemes discussed above could become ineffective when DRAM scales to high densities or workloads become memory-intensive. Therefore, we propose RPC to mitigate refresh overhead.

# 2.3 Architecture and Design

#### 2.3.1 DRAM Refresh Characterization

A DRAM-based memory system usually consists of multiple ranks. Each rank works independently even though all of the ranks share the same channel bandwidth. Commodity DRAM refreshes at rank level. The memory controller issues a refresh command to a rank every tREFI. Each refresh operation lasts for a duration of tRFC.

Fig. 3. Staggered refresh in ranks within the same channel.

Thus the available time interval between two contiguous refresh operations equals to tREFI-tRFC. When a rank receives a refresh command from memory controller, all banks in the rank are refreshed concurrently. Therefore, no memory access is allowed to a rank where a refresh is undergoing. Fortunately, only one rank is allowed to be refreshed at a time to meet power budget. All ranks in the same channel are refreshed in a staggered fashion, as shown in Figure 3. There is no time overlap between different refresh commands occurred to different ranks. In this case, other ranks in the same channel can still service DRAM accesses normally when one rank is being refreshed. However, a request arriving at the rank which is being refreshed still needs to wait until the refresh operation completes, which increases the read latency. In the worst case, the waiting time is tRFC, which is an order of magnitude longer than a typical read response. Hence, system performance is degraded significantly and the longer running time in turn increases static energy consumption. It is increasingly important to mitigate refresh overhead.

#### 2.3.2 The RPC Architecture

The design goal of RPC is to alleviate refresh overhead by serving memory requests and refresh operations that are issued to the same rank in parallel. Since ranks in the same channel are refreshed in a staggered manner, the remaining ranks

Fig. 4. The RPC architecture. The to-be-read data is cached in an adjacent rank before the target rank is locked and each rank reserves or over-provisions a cache region to store the cached data. All cache regions are organized in a rotated fashion.

in the same channel are still available when a rank is being refreshed. Based on this DRAM characteristic, we propose RPC to mitigate refresh overhead. The idea is to cache those data which will be read during the next refresh period, and store it to an adjacent rank before the target rank is locked. The data is populated to the cache in a piggyback manner in which data is cached when it is accessed, rather than prefetching it to the cache in the adjacent rank in a bursty fashion. In our design, only read requests are taken into consideration and this is due to two reasons: 1) read requests are latency sensitive because applications cannot proceed until data is retrieved; 2) write requests can be cached in a write buffer and flushed to memory in batches asynchronously. The design of RPC is shown in Figure 4. Each rank reserves or over-provisions an area, called a cache region, to store the cached data; the size of the cache region is a configurable parameter in later performance evaluations so that we can gauge the impact of cache size. The cache region placed on rank i only services memory requests addressed to its previous rank i - 1, and all cache regions are organized in a rotated fashion. In particular, cached data from the last rank, N - 1, is stored at rank 0. When a read request arrives at a rank where a refresh is undergoing, the memory controller first checks the cache region in the "next" rank in the same channel; if the required data is cached, the memory controller can serve

the read request without waiting for the refresh operation to complete, which reduces refresh overhead and improves system performance. However, the effectiveness of RPC depends on cache hit ratio.

## 2.3.3 Cache Design

As shown in Figure 4, the CPU sends requests to the memory controller in the form of transactions. First, a transaction is enqueued into the transaction queue if there is spare space; then it is translated into DRAM commands (e.g. ACT, CAS, PRE etc.) and enqueued into the command queue. To achieve high row hit ratio, modern memory controllers commonly adopts FR-FCFS (first-ready first-come-firstserve) scheduling policy [29], which prioritizes DRAM commands that cause row hits over other commands, including those that were issued earlier. If no command results in a row hit, then FR-FCFS schedules commands according to arrival sequence, i.e., FCFS. A key advantage of this scheduling policy is that it retains the temporal locality in the application access pattern. Meanwhile, the row hit ratio is also related to the address mapping policy. In this work, we use the "channel:row:column:bank:rank"address mapping policy, which is commonly deployed in state-of-the-art memory controllers. In this address mapping, the row bits are placed as MSBs to maximize the row hit ratio while keeping ranks and banks interleaving. We run the full PARSEC benchmark suite to observe the memory access locality. For brevity, three representative benchmarks are chosen to be shown in Figure 5a, and other benchmarks have similar results as the ferret benchmark. The Y axis represents the relative row number in a channel, which can be calculated by Equation 2.1. Notations used in the equation are listed in Table 3.

(a) Access locality of three representative benchmarks.

(b) Access locality of the *cannel* benchmark in each rank.

Fig. 5. Access locality of PARSEC benchmark suite running on two-rank DRAM system. X-axis represents access sequence and Y-axis is the row number calculated by Equation 2.1. 100 consecutive memory accesses are randomly chosen to show.

$$row\_num = NUM\_ROWS * NUM\_BANKS * rank + NUM\_ROWS * bank + row$$

$$(2.1)$$

All benchmarks show very strong temporal locality except *canneal*, which shows poor access locality. However, the cache region is only used for the to-be-refreshed rank instead of the global scope (i.e. the whole channel). We further break down

Table 3. Notations used in Equation 2.1.

| Variables | Description                        |

|-----------|------------------------------------|

| NUM_ROWS  | the total number of row in a bank  |

| NUM_BANKS | the total number of bank in a rank |

| rank      | accessed rank number               |

| bank      | accessed bank number               |

| row       | accessed row number                |

| row_num   | relative row number in a channel   |

the access pattern of *canneal* benchmark and study the locality of data access on each individual rank. From Figure 5b, we can observe that the temporal locality in each rank is also good even though the overall perceived temporal locality is poor. All of these memory accesses happen after the LLC (last level cache), although some of them have good temporal locality, which means all accesses are missed in the LLC. That is because the size of a row is much larger than a CPU cache line, and a row typically contains 16 to 32 CPU cache lines. Therefore, it is possible that the successive requests access different CPU cache lines but the same DRAM row.

Based on the above observations, DRAM accesses have a strong temporal locality, which means recently accessed rows will likely be accessed again in the near future. Therefore, the cache region is implemented as a LRU (Least Recently Used) cache, where the least recently used data will be evicted and recently accessed data will be saved. We note that the cache region is different from caches in the CPU. CPU caches are used to speed up accesses while the cache region in RPC is used to increase data availability during the interval when the target rank is being refreshed, and the entire cache region will be invalidated after the refresh completes. As mentioned in Section 2.2, the granularity of read/write operations in a bank is a DRAM row, thus the size of a cache line is set to the same as the size of a DRAM row (i.e. page size). As shown in Figure 3, the piggyback caching is executed during the available time

LRU algorithm, in which only recently accessed rows will be cached, we start the piggyback caching a number of cycles ahead of next refresh operation, and end at the beginning of next refresh operation. This time interval is called the caching interval, the length of which is referred to as tCI. The tCI is also configurable. For example, a rank starts to be refreshed at t, the next refresh operation will start at t+tREFI. So the piggyback caching begins at t+tREFI-tCI, and ends at t+tREFI. Algorithm 1 shows the pseudocode of RPC in each rank.

# 2.3.4 Implementation Overhead

To implement *RPC*, each rank needs to have a dedicated cache region or be over-provisioned to accommodate cached data, and the size of it should be an integer multiple of the page size. To track which row is cached, the memory controller also needs to maintain a tag list for each cache region. Each entry is a 64-bit physical address which consists of the channel number, rank number, bank number, row number and column number. The number of entries in each tag list equals to the cache size divided by the page size (i.e. the total number of rows in the cache region). Therefore, the total storage overhead in the memory controller is determined by the cache size, the number of ranks in a channel, and the number of channels. For example, in a single channel and four-rank DRAM system, if the cache size is 16KB and the page size is 1KB, then the total storage overhead in the memory controller is 512 bytes, which is negligible. In addition, copying data to an adjacent rank consumes energy. However, the energy consumption is negligible due to the short caching interval, as demonstrated in Section 2.4.2. *RPC* can reduce the runtime of applications, as a result, it reduces the static energy consumption of DRAM system.

# **Algorithm 1** The work procedure of *RPC*

```

Input: tCI, cache size

Variables: curretn time t, next refresh time tNR

1: while DRAM is running do

2:

while tNR - tCI \le t < tNR do

▷ caching start

3:

if a memory request comes then

4:

if the accessed row is cached then

5:

move the cache line to list head:

6:

else

7:

if cache region is not full then

8:

copy the accessed row to a spare cache line;

9:

inset the cache line to list head;

10:

else

11:

invalidate the tail cache line:

12:

copy the accessed row to the tail cache line;

13:

insert the last cache line to list head;

14:

end if

15:

end if

16:

end if

17:

t++;

18:

end while

▷ caching over

19:

while tNR \le t < tNR + tRFC do

▷ refresh start

20:

if a memory request comes then

21:

if it is a read request then

22:

if the required row is cached then

23:

return the cache line to the CPU;

24:

else

25:

wait until the refresh is completed;

26:

end if

27:

else

28:

handled normally;

29:

end if

30:

end if

31:

t++;

32:

end while

⊳ refresh over

33:

if t \ge tNR + tRFC then

34:

invalidate the entire cache region;

35:

tNR = tNR + tREFI;

36:

end if

37:

memory requests are handled normally;

38:

t++;

39: end while

```

# 2.4 Evaluation

# 2.4.1 Evaluation Methodology

To evaluate the effectiveness of our approach, we implement RPC in DRAMSim2 [26] and together use MARSSx86 [30] as the front-end processor to run benchmarks. The detailed system configuration is shown in Table 4. The PARSEC 2.1 [27] and SPLASH-2 [28] benchmark suites are used to evaluate our approach. Both of them are multi-thread and memory-sharing benchmark suites. We run all benchmarks for 100 million cycles to warm up the cache and the following 100 million cycles to collect the statistics. The 8Gb DRAM chip is used in our evaluation, and the DRAM chip parameters are set according to the Microns data sheet [22]. The refresh related parameters are listed in Table 1. All simulations are run under normal temperature range ( $\leq 85$  °C). The instructions-per-cycle (IPC) is used as the performance metric throughout the evaluation.

Table 4. Configuration of Simulators.

| Processor            | 1/4 cores, 4GHz, out-of-order<br>128-entry instruction window                                                                           |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| L1-D/L1-I Cache      | 128KB/128KB, 8-way associative                                                                                                          |

| LLC                  | 64B cache-line, 8-way associative shared, 2MB                                                                                           |

| Memory<br>Controller | 32/32-entry transaction/command queue<br>FR-FCFS [29], open page policy, 64bits I/O bus<br>channel:row:column:bank:rank address mapping |

| DRAM                 | DDR3-1333 [22], 8Gb<br>1 channel, 2/4 ranks per channel<br>8 banks/rank, 128K rows/bank, 1024 columns/row                               |

For comparisons, we also implement state-of-the-art FGR [12] and No Refresh refresh schemes in DRAMSim2. The FGR includes three different refresh modes with different refresh rates, which are 1x, 2x and 4x modes. Note the 1x mode is

the conventional refresh scheme in modern memory controllers. The refresh related parameters of each mode are listed in Table 2. The *No Refresh* scenario is an ideal case where there is no refresh operation. The reason for assessing *No Refresh* is to quantify the best possible performance in terms of IPC. In the runs, we also vary the number of ranks since our design targets rank-level caching and this parameter has a large impact on the overall system performance. As multi-core becomes increasingly prevalent as a means to further increase flops and hence main memory can be shared by multiple cores, contention in the memory system is anticipated to be more severe. Therefore in the evaluations, we also test a four-core scenario to gauge the scalability of our approach.

## 2.4.2 Design Space Exploration

In our design, both the size of cache region (a.k.a. cache size) and the length of caching interval (tCI) are configurable. As the system performance and overhead are sensitive to these two parameters, we conduct a design space exploration to determine the optimal values for the two parameters before the performance evaluation. The PARSEC 2.1 benchmark suite is used to evaluate. To determine the optimal cache size, memory controller starts caching data at the end of last refresh (i.e. tCI = tREFI - tRFC). As shown in Figure 6, with 8KB, 16KB and 32KB cache region, RPC improves the system performance by 4.9%, 8.1% and 8.6% on average, respectively. To balance between hardware cost and performance, 16KB is used as the optimal value for cache size, which is equivalent to 16 rows. Based on the optimal cache size, we test three different values of tCI, which are integer multiple of the refresh cycle (tRFC). As shown in Figure 7, the 1xtRFC tCI is sufficient to achieve almost all the performance margin due to the usage of LRU cache algorithm and the limited cache size. Therefore, 1xtRFC is chosen as tCI for subsequent runs.

Fig. 6. The performance of RPC with various cache size, normalized to the 1x mode refresh scheme.

Fig. 7. The performance of RPC with various tCI, normalized to the 1x mode refresh scheme.

## 2.4.3 Single-Core Simulation Results

With the optimal cache size and the length of the caching interval (tCI), we next compare RPC to FGR and No Refresh schemes. All benchmarks are run on a single-core and single-thread system, and the evaluation results with regard to the different number of ranks are shown in Figure 8. It is clear that for all benchmarks

Fig. 8. Performance comparisons among FGR, RPC and No Refresh schemes with various number of ranks in a single-core system. RPC outperforms all FGR modes and improves system performance by 8.1% (8.7%) and 9.6% (10.8%) on average for PARSEC and SPLASH-2 benchmark suites in the two-rank (four-rank) system, respectively.

there is a large performance gap between 1x mode and No Refresh. Compared to No Refresh, the geometric mean of performance degradation is 17.4% (PARSEC) and 23.9% (SPLASH-2) for a two-rank system, and 13.7% (PARSEC) and 12.7% (SPLASH-2) for a four-rank system. In particular, the performance degradation of ocean\_noncont benchmark is up to 48.5%. From these results we have two observations. First, most benchmarks in these two benchmark suites are memory-intensive workloads and memory system design has a huge impact on application performance. Second, conflicts between accesses and refreshes are reduced as the number of rank increases, because less memory requests go to each rank comparing to two-rank sys-

tems. As a result, the performance of 2x and 4x modes are worse than that of the 1x mode in most cases. And the performance of 2x and 4x modes in the four-rank system is better than that in the two-rank system.

It is shown in Figure 8 that RPC outperforms all FGR modes, because it can serve memory requests and refreshes concurrently while FGR becomes ineffective for the memory-intensive workloads as discussed in Section 2.2.3. RPC improves the system performance by 8.1% (8.7%) and 9.6% (10.8%) on average for PARSEC and SPLASH-2 benchmark suites in the two-rank (four-rank) system, respectively. And RPC is comparable to the ideal case (around 95% of No Refresh). However, the performance improvement of canneal is less than 1% due to the poor temporal locality as shown in Figure 5a.

#### 2.4.4 Four-Core Simulation Results

All runs are repeated on a four-core system with one thread per core to gauge the effectiveness in a multi-core environment, and the evaluation results with regard to the different number of ranks are shown in Figure 9. Since memory access becomes more intensive in these runs, comparing 1x mode to No Refresh, the performance degradation increases to 26.9% (15.2%) and 25.5% (14.4%) on average for PARSEC and SPLASH-2 benchmark suites in the two-rank (four-rank) system, respectively. On average, the performance of both 2x mode and 4x mode are worse than the 1x mode as expected. In contrast, RPC improves the system performance by 10.7% (8.6%) and 9.3% (12.2%) on average for these two benchmark suites in the two-rank (four-rank) system, respectively. And RPC can still achieve around 93% performance of No Refresh scheme, thus RPC scales very well in the multi-core environments.

Fig. 9. Performance comparisons among FGR, RPC and No Refresh schemes with various number of ranks in a four-core system. RPC outperforms all FGR modes and improves system performance by 10.7% (8.6%) and 9.3% (12.2%) on average for PARSEC and SPLASH-2 benchmark suites in the two-rank (four-rank) system, respectively.

## 2.5 Related Work

Refresh Reduction. Ghosh et al. [31] proposed *Smart Refresh* to eliminate unnecessary refresh operations. It leverages the characteristics that a read/write is equivalent to refresh due to the destructive access. Each row is bounded to a counter which gets reset whenever the row gets read out or written to. However, *Smart Refresh* requires very high storage overhead in the memory controller (e.g. up to 1.5MB in a 32GB memory system) [32], [33], and its effectiveness depends on the working set. *RAIDR* [32] proposed by Liu et al. also aims to reduce the number of refreshes. *RAIDR* uses the knowledge of cell retention times to group DRAM

rows into retention bins and applies different refresh rates to different bins. As a result, rows containing leaky cells are refreshed at a normal rate, while most rows are refreshed less frequently. However, this retention-aware approach requires an accurate retention time profile which is hard to be determined due to the *Variable Retention Time (VRT)* [34, 35, 36].

Some software solutions were also devised to reduce refreshes. RAPID proposed by Venkatesan et al. [37] exploits retention time variations among different DRAM cells. The pages with longer retention time are allocated with priority over those with shorter retention time. The refresh rate is determined by the page with the shortest retention time among all allocated pages. However, RAPID has the same risk as RAIDR due to the variation in retention time, which may cause data reliability issue. In addition, its effectiveness depends on the utilization of the memory pages. Flikker [38] is another software solution to save refresh power by reducing the number of refreshes. In Flikker system, data is divided into critical and non-critical data. The portion of memory containing critical data is refreshed at the regular refresh rate, while the other is refreshed at a much lower rate to save power, which inevitably leads to retention errors. However, Flikker requires substantial modifications (to application, OS, DRAM chips) to implement it. All of the above mentioned refresh reduction solutions are orthogonal to our approach.

Refresh Pausing. Nair et al. [18] proposed Refresh Pausing to alleviate refresh overhead by allowing refresh operations to be interruptible. As a result, memory requests arriving during the refresh period can be serviced in a timely manner via pausing the on-going refresh operation. However, refresh operations have to be paused and resumed very frequently under memory-intensive workloads. In addition, the refresh operations become uninterruptible if DRAM rows are refreshed in a staggered or pipelined way [33].

Refresh Scheduling. Elastic Refresh (ER) [1] is proposed to mitigate refresh overhead. It leverages the refresh scheduling flexibility: up to eight refresh commands can be postponed. The basic idea is to avoid interferences between DRAM refreshes and memory requests that come outs during refresh periods by postponing the refresh commands for a predicted time period, which is based on the average idle period of a rank and the number of postponed refresh commands. In contrast to DUE [24], ER defers the refresh commands even when the to-be-refreshed rank is idle. However, ER becomes less effective under memory-intensive workloads since the average rank idle period is too short to hide the refresh period. Moreover, ER can adversely incur extra delay when it incorrectly predicts a time period as idle as discussed in Section 2.2.3.

Mukundan et al. [33] propose Delayed Command Expansion (DCE) and Preemptive Command Drain (PCD) respectively, to mitigate refresh overhead. DCE intentionally withholds admission of memory requests into the command queue if the target rank is being refreshed to prevent them from wasting command queue resources. PCD prioritizes commands that map to the to-be-refreshed rank to drain these commands before the rank is refreshed. In doing so, PCD can make more room for other commands that map to other ranks, thereby increasing parallelism among ranks during refresh period.

Concurrent Refresh. Chang et al. [25] and Zhang et al. [23] proposed concurrent refresh mechanisms, both of which increase the refresh granularity to a subarray so that refreshes and accesses can be serviced concurrently in different subarrays in the same bank. RPC distinguishes itself from those concurrent architectures in the following respects. First, our solution does not rely on the underlying DRAM organization and can be applied to a broad category of DRAM organizations. Second, it is hard to eliminate conflicts completely between accesses and refreshes as each subarray

contains dozens of rows. Bursty conflicts might happen when workloads have strong locality as shown in Section 2.3.3. In contrast, depending on the caching policy and cache size, RPC is able to reduce the probability of conflict between memory access and refresh to a lower level.

## **CHAPTER 3**

## ARCHITECTING DIE-STACKED DRAM AS A PART OF MEMORY

#### 3.1 Introduction

Recent advances in die-stacking technology have made it possible to integrate a large amount of DRAM in the same package of a processor. A processor and onchip DRAM are interconnected by a high-density, low-latency through-silicon vias (TSVs). This technology has the potential to overcome the memory wall problem [3] by providing an order of magnitude higher bandwidth and much lower latency for onchip DRAM. Prior work [39, 40, 41, 42, 43, 44] has proposed using die-stacked DRAM as a hardware-managed last-level cache (i.e., DRAM cache). As the technology for manufacturing die-stacked DRAM matures, the size of die-stacked DRAM could be tens of gigabytes by integrating multiple DRAM stacks on a 2.5D interposer [45, 46]. Therefore, using die-stacked DRAM as a DRAM cache would squander a large fraction of total memory space as the DRAM cache is invisible to the OS. Without fully exploiting the memory capacity offered, applications with a large working set would suffer a higher rate of page faults and therefore slowdown due to frequent accesses to backend storage.

An alternative to using die-stacked DRAM as a cache is to use it as part of an OS-visible memory space (i.e., PoM). In such a heterogeneous memory system, data residing in on-chip DRAM is serviced at high bandwidth and low latency, while data residing in off-chip DRAM is serviced at low bandwidth and high latency. However, naively treating on-chip DRAM as a part of memory space renders the PoM design less effective. To obtain high performance, on-chip DRAM needs to play two roles at the

same time in a PoM architecture. The on-chip DRAM is not only a part of memory space but also a cache for off-chip DRAM. In other words, requested data is swapped or migrated to on-chip DRAM and victim data is swapped out to off-chip DRAM. This swapping process can be done by either the OS or hardware. For OS-managed approaches, the OS needs to monitor all page usage and migrate hot pages to the on-chip DRAM. OS-invoked page migrations result in page table updates and TLB shoot-downs, which are costly operations. Therefore, the page migrations under the OS control cannot occur frequently so that hot pages in a short period of time could not be migrated to the on-chip DRAM, resulting in performance loss. In contrast, in a hardware-managed PoM architecture, the migration is transparent to OS, and can be initiated at anytime when data is required. Hence, the hardware-managed PoM is a promising design and we only consider hardware-managed PoM in this work.

Current PoM designs [47, 48] fall into two categories based on the granularity at which they swap data: line-based and page-based (or segment-based). The line-based design uses off-chip bandwidth efficiently as all swapped lines are demanded. However, the line-based design could suffer from low hit ratio due to poor temporal locality at the main memory layer as highly referenced cache lines have already been filtered out by L1 and L2 caches. The page-based design swaps data at a coarser granularity (typically 1-4KB), thus achieving a higher hit ratio by exploiting spatial locality in the large granularity. However, the page-based design would waste precious off-chip bandwidth as some lines may not be touched before they are swapped out. The inefficient usage of off-chip bandwidth could lead to performance degradation, especially for data-intensive applications.

To take advantage of both line-based and page-based PoM designs while avoiding their respective drawbacks, we propose SELF [49], a high performance and memory bandwidth efficient approach to using die-stacked DRAM as a part of memory. SELF only swaps those lines in a requested page that are likely to be accessed according to its page footprint. In doing so, SELF enables most incoming requests to be serviced from on-chip memory while avoiding swapping unused lines to save memory bandwidth.

### 3.2 Background and Motivation

As more cores are integrated into many-core chips to improve processing capabilities and parallelism, the growth in core count requires a commensurate increase in memory bandwidth. However, memory speeds have not kept pace with CPU performance scaling, which has led to the memory wall problem [3]. Die-stacked DRAM has been advocated as a promising technology to break the memory bandwidth and latency wall. It provides an order of magnitude higher bandwidth and lower access latency than off-chip DRAM due to the dense TSVs buses [50]. However, the capacity of die-stacked DRAM is insufficient to fully replace off-chip DRAM due to technological constraints [41, 48]. Thus, die-stacked DRAM and off-chip DRAM will co-exist in future systems, and die-stacked DRAM can be used either as a cache or as a part of main memory. Most prior work [40, 41, 42, 43, 44, 51, 52, 53] advocates using die-stacked DRAM as a giant cache between the last level cache (LLC) and main memory, and copes with challenges of tag storage overhead, hit ratio, hit/miss latency and off-chip traffic etc. However, DRAM cache is invisible to the OS. In other words, DRAM cache cannot contribute towards the main memory capacity, which could lead to non-negligible performance loss due to increased page faults, especially for modern server applications with a large working set size (WSS). As the technology for manufacturing die-stacked DRAM matures, the size of die-stacked DRAM in each package could be up to tens of gigabytes. In this case, using die-stacked DRAM as a cache could waste a large fraction of total memory space.

Therefore, researchers have proposed using die-stacked DRAM as a part of mem-

ory [48, 47, 54, 55] instead of a cache. However, we can only get marginal benefits if the die-stacked DRAM is naively treated as a part of memory [55]. To obtain high performance, highly referenced pages or lines need to be migrated to die-stacked DRAM to take advantage of its high bandwidth and low access latency. This migration process can be performed by the OS or hardware.

### 3.2.1 OS-managed PoM

OS-managed PoM approaches need to track page usage to identify highly referenced pages. For an on-chip DRAM with a capacity of N pages, the OS should choose the top-N most referenced pages and map them into the on-chip memory at run-time. However, the operating system has a limited capability to get such information from the page table as the reference bit in each page table entry (PTE) cannot differentiate which pages are most referenced. A typical solution is to use a counter in each PTE to record the number of LLC misses per page, which would require extra hardware support [56]. At the end of each epoch or interval (e.g. 100K cycles), the OS sorts pages based on the access count and migrates the top-N hottest pages which are resident in off-chip memory to the on-chip memory. At the same time, these pages which are resident in on-chip DRAM but not belonging to the top-N hottest pages are migrated back to off-chip DRAM. Then the OS has to update the page table to reflect new mappings and invalidate corresponding translation lookaside buffer (TLB) entries (i.e., TLB shoot-down) for consistency. Therefore, the data migration under the OS control results in high overhead of sorting, copying pages back and forth between on-chip and off-chip memories, and TLB shoot-downs. As such, OS-managed migration cannot be performed frequently, which could miss many opportunities to improve performance by migrating pages that are highly referenced in short periods of time. In addition, OS-managed data migration can only occur at a page granularity (typically 4KB). When a significant fraction of data lines are not referenced, such page granularity transfers become very inefficient in terms of off-chip memory bandwidth. In a word, OS-managed PoM approaches could neither exploit the full benefits of on-chip DRAM at a coarse-grained interval nor utilize the off-chip memory bandwidth efficiently at a page granularity.

### 3.2.2 Hardware-managed PoM

Hardware-managed PoM can avoid page table updates, TLB shoot-downs and page sorting by maintaining a hardware-managed remapping table, which records real locations after swapping. The remapping table is updated by hardware without involving the OS after each data migration completes. Hence, the data migrations under hardware control could occur whenever the requested data is not resident in the on-chip memory, which could potentially improve the system performance. According to swapping granularity, hardware-managed PoM designs fall into two categories: line-based and page-based.

#### 3.2.2.1 Line-based PoM