# Virginia Commonwealth University VCU Scholars Compass

Theses and Dissertations

**Graduate School**

2020

# Systematic Model-based Design Assurance and Property-based Fault Injection for Safety Critical Digital Systems

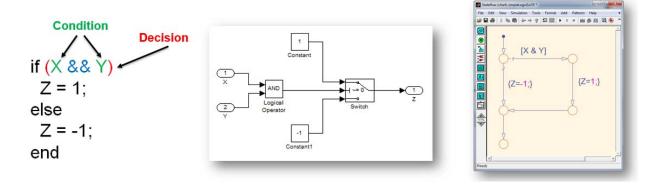

Athira Varma Jayakumar

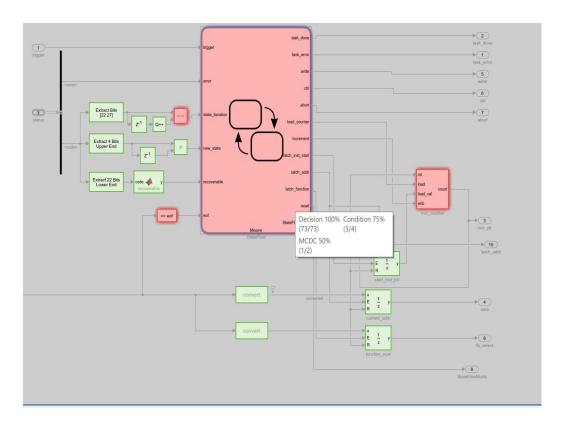

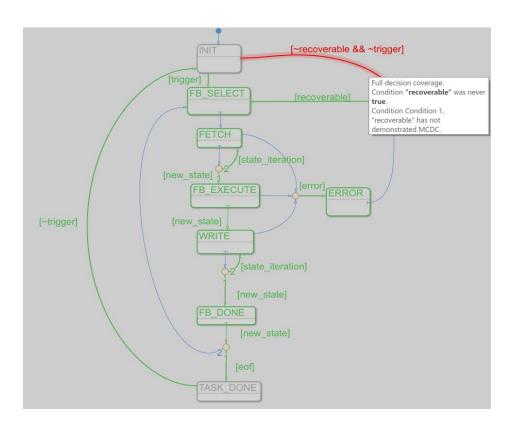

Follow this and additional works at: https://scholarscompass.vcu.edu/etd

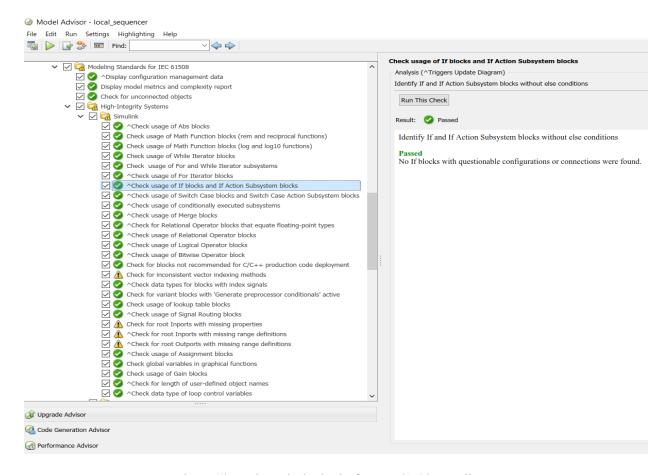

Part of the Computational Engineering Commons, Computer and Systems Architecture Commons, Digital Circuits Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons

© The Author

#### Downloaded from

https://scholarscompass.vcu.edu/etd/6239

This Thesis is brought to you for free and open access by the Graduate School at VCU Scholars Compass. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of VCU Scholars Compass. For more information, please contact <a href="mailto:libcompass@vcu.edu">libcompass@vcu.edu</a>.

# Systematic Model-based Design Assurance and Propertybased Fault Injection for Safety Critical Digital Systems

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Engineering with a concentration in Electrical and Computer Engineering at Virginia Commonwealth University

by

#### ATHIRA VARMA JAYAKUMAR

Bachelor of Technology, Electronics & Communication Engineering, Cochin University of Science and Technology, India, 2009

Director: Dr. CARL R ELKS

Associate Professor, Department of Electrical and Computer Engineering

Virginia Commonwealth University

Richmond, Virginia

May, 2020

#### Acknowledgement

First and foremost I would like to express my sincere gratitude to my advisor Dr. Carl R Elks, for offering me an excellent opportunity to work in his lab as Graduate assistant which helped me gain a lot of knowledge and valuable experience and helped to cultivate in me the talent of conducting scientific research. His immense knowledge, guidance and motivation helped me achieve the goals in my research and to complete my thesis successfully. He has always been very supportive and understanding and I am extremely blessed to have him as my advisor. I also sincerely thank Dr Ashraf Tantawy and Dr Alen Docef for serving on my thesis committee and providing me valuable feedback and support.

I would like to thank Department of Energy, Division of Advanced Sensors and Instrumentation (DOE-ASI) and Electric Power Research Institute (EPRI) who funded the SymPLe architecture project, which is the representative architecture used for the study presented in this thesis manuscript. I would also like to wholeheartedly thank the Project PI, Matt Gibson of EPRI for all his support during my work in SymPLe project.

I would like to extend my gratitude to all my colleagues in the SymPLe architecture project Smitha Gautham, Richard Hite, Christopher Deloglos and Dr Ashraf Tantawy for all the stimulating discussions we had together, valuable suggestions on my work and all the help you granted me. I would like to express special thanks to Smitha Gautham for becoming a very close friend of mine and for making my stay here at VCU a homely and pleasant experience.

I would also like to express my sincere thanks to Ken Thomas of Idaho National Laboratories, Department of Energies for providing me an opportunity to be part of the valuable study on Bounded Exhaustive Testing to address Software common cause failures. I am also privileged to have got a chance to collaborate with Dr. Richard D Kuhn and Dr Raghu N Kacker of National Institute of Standards and Technology (NIST). I am grateful for your guidance and support on the study on combinatorial testing. I would like to thank my teammates Aidan Collins, Brandon Simon and Anastasios Karles for helping me in my work in the Bounded Exhaustive testing project.

I am grateful to all my teachers for the wisdom they shared, their guidance and blessings. I would also like to extend immense gratitude to my dear parents Kala and Jayakumar for raising me with love, providing me a wonderful childhood and education and constantly supporting and encouraging me. I would not have been able to reach where I am today, without their support and blessings. I would also like to sincerely thank my parents-in-law Geetha and Vijayakumar whose blessings, constant prayers and encouragement helped me to successfully complete my studies. I would like to thank my late paternal grandparents Thankamani and Kerala Varma for all their blessings and unconditional love they showered on me. I would also like to thank my maternal grandparents Bhadramani and Rama Varma who continues to pray for me and offer me endless love. I also thank my sisters Aswathy and Sangeetha who have always been there for me and praying for all success and happiness in my life. I would also like to thank my brothers-in-law Ajithnath and Anand for all their good wishes.

Last but never the least, I would like to thank my dear husband Jayakrishnan and my loving daughter Gauri for all their support and help during my studies. They had been very understanding to offer me all the time I needed to work on research, prepare for my exams and work on assignments. I am extremely grateful to my loving and caring husband for always encouraging me and wholeheartedly wishing for my excellence in any endeavor I take over.

# **Table of Contents**

| List of Figures                                            | 6  |

|------------------------------------------------------------|----|

| List of Tables                                             | 8  |

| List of Abbreviations                                      | 9  |

| Abstract                                                   | 11 |

| Chapter 1 Introduction                                     | 13 |

| 1.1 Motivation                                             | 13 |

| 1.2 Complexity in Software Based Systems                   | 14 |

| 1.3 Early Detection of Systematic Failures                 | 15 |

| 1.4 The Role of Standards                                  | 15 |

| 1.5 Summary                                                | 16 |

| 1.6 Outline                                                | 17 |

| Chapter 2 Background                                       | 18 |

| 2.1 Concepts of Dependability                              | 18 |

| 2.2 Impairments or Threats to Dependability                | 19 |

| 2.3 Important Principles for Safety Critical Systems       | 22 |

| 2.4 Fault Avoidance and Fault Tolerance Concepts           | 23 |

| 2.5 Fault Injection                                        | 24 |

| 2.6 Contributions                                          | 26 |

| Chapter 3 Related Work                                     | 27 |

| Chapter 4 Overview of the Representative System            | 30 |

| Chapter 5 Model Based Engineering and Design Assurance     | 33 |

| 5.1 Model-based Engineering and Design                     |    |

| 5.2 Model Based Design Assurance                           | 35 |

| 5.3 Choice of MBD Tool                                     | 36 |

| 5.4 Development of a model based design assurance workflow | 37 |

| 5.5 Model Testing                                          | 43 |

| 5.5.1 Hierarchy of Model Testing                           | 45 |

| 5.5.2 Simulink Tool Major Features to assist model testing | 46 |

| 5.6 Test Oracle Specification                              | 49 |

| 5.7 Test Inputs Specification                              | 50 |

| 5.7.1 Sequence Based Testing                               | 51 |

| 5.7.2 Boundary Value Combinatorial testing:                                            | 56  |

|----------------------------------------------------------------------------------------|-----|

| 5.8 Test Execution                                                                     | 58  |

| 5.9 Test Results Analysis in MBD                                                       | 59  |

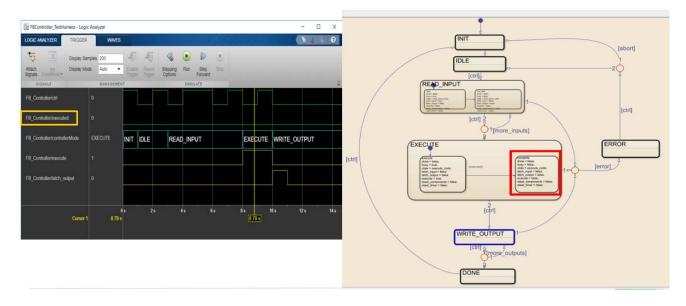

| 5.9.1 Analysis using Logic Analyzer                                                    | 59  |

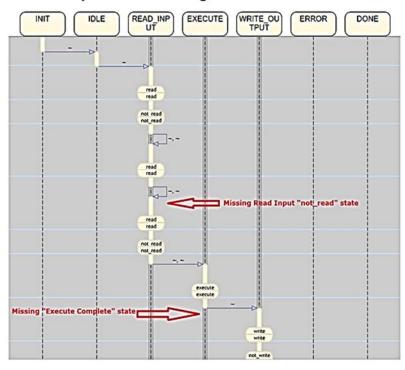

| 5.9.2 Analysis using Animations                                                        | 63  |

| 5.9.3 Analysis using State Sequences                                                   | 64  |

| 5.9.4 Analysis using Single step Execution                                             | 66  |

| 5.10 Integration Testing                                                               | 68  |

| 5.11 System Testing                                                                    | 70  |

| Chapter 6 Model Coverage Analysis Workflow                                             | 73  |

| 6.1 Functional Coverage                                                                | 74  |

| 6.2 Structural Coverage                                                                | 76  |

| 6.3 Reasons for Low Model Coverage                                                     | 80  |

| Chapter 7 Static Verification                                                          | 82  |

| 7.1 Static Conformance to IEC 61508                                                    | 82  |

| 7.2 Design Error Detection                                                             | 84  |

| 7.2.1 Example: Dead Logic Detection                                                    | 85  |

| Chapter 8 Findings on Model-based Design Assurance                                     | 86  |

| 8.1 Design Flaws detected during Model based V&V                                       | 86  |

| 8.2 Lessons Learnt during the Model-based Design Assurance workflow                    | 88  |

| Chapter 9 Model Based Fault Injection                                                  | 92  |

| 9.1 Introduction                                                                       | 92  |

| 9.2 Background                                                                         | 92  |

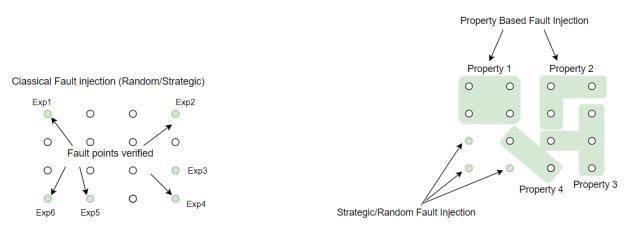

| 9.3 Classical Fault injection and Strategic Fault Injection                            | 93  |

| 9.4 Strategic Fault Injection                                                          | 97  |

| 9.5 Introduction to model checking                                                     | 98  |

| 9.5.1 Property Coverage: Do I have all of the Properties                               | 100 |

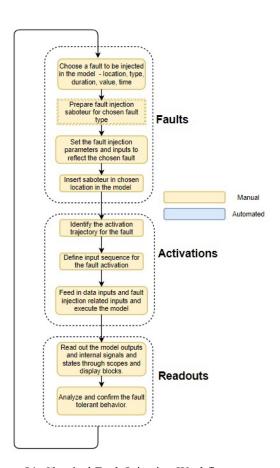

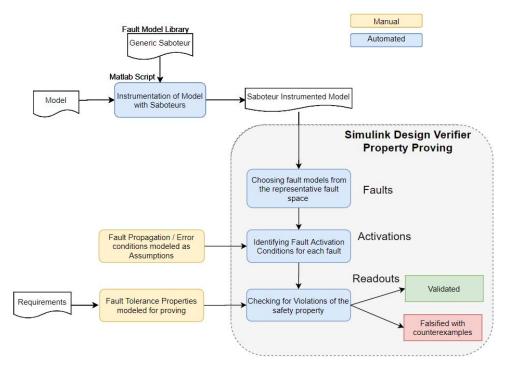

| 9.6 Model Based Fault Injection using Property Proving                                 | 101 |

| 9.6.1 Challenges with Property based fault injection                                   | 105 |

| 9.6.2 Classical Fault Injection vs Property based fault injection.                     | 106 |

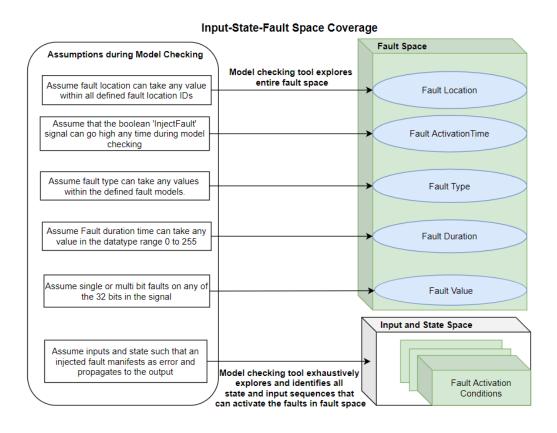

| 9.6.3 Property Based fault injection - Fault-Input-State space Coverage                | 110 |

| 9.7 Design and Implementation of a Comprehensive Fault Injection Framework in Simulink | 112 |

| 9.7.1 Faults and Fault Model                                                           | 112 |

| 9.7.2 Saboteurs                                                                        | 113 |

| 9.7.3 Automated Saboteur insertion in model                                                | . 117 |

|--------------------------------------------------------------------------------------------|-------|

| 9.8 Application of Property Based Fault Injection                                          | . 119 |

| 9.8.1 Use case 1- Verifying Failure Semantics of SymPLe Function Blocks                    | . 120 |

| 9.8.2 Use case 2 - Verifying Timeout functionality during SymPLe Function Blocks Execution | . 124 |

| 9.8.3 Efficiency Comparison between Classical and Property-Based FI                        | . 126 |

| Chapter 10 Conclusions and Future Work                                                     | 128   |

| References                                                                                 | 129   |

| Appendix                                                                                   | 134   |

# **List of Figures**

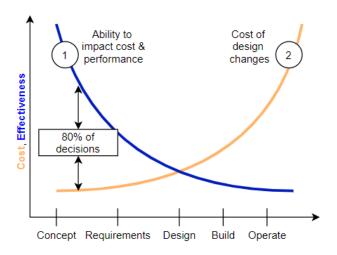

| Figure 1: Decision Effectiveness during life cycle (adapted from [9])[9]                               | 15  |

|--------------------------------------------------------------------------------------------------------|-----|

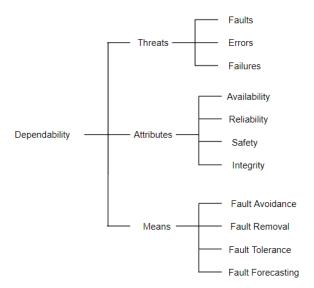

| Figure 2: Taxonomy of Dependability[14]                                                                |     |

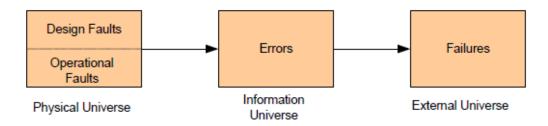

| Figure 3: Three Universe Model [2]                                                                     |     |

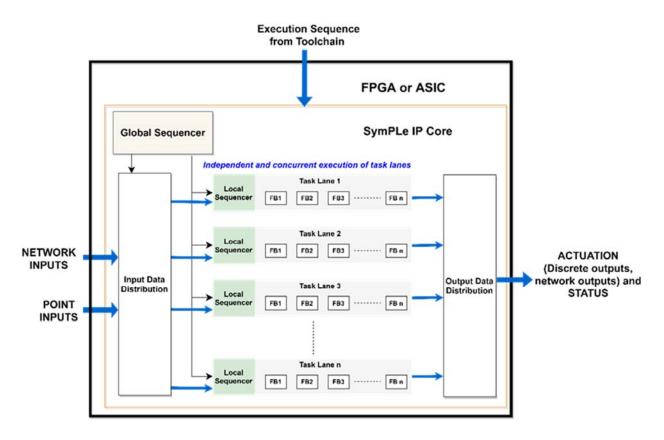

| Figure 4: The SymPLe Architecture [42]                                                                 | 31  |

| Figure 5: Fault Tolerance Approach for SymPLe [51]                                                     | 32  |

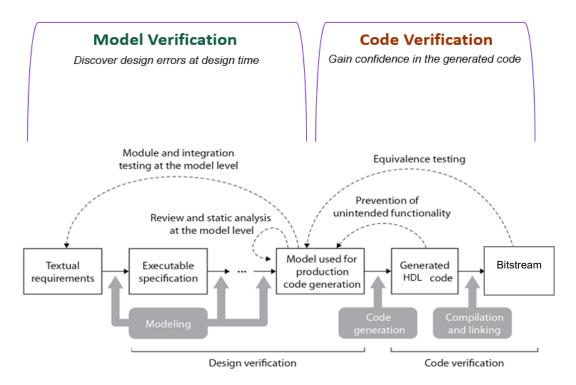

| Figure 6: Model-based Design Verification Workflow [54]                                                | 36  |

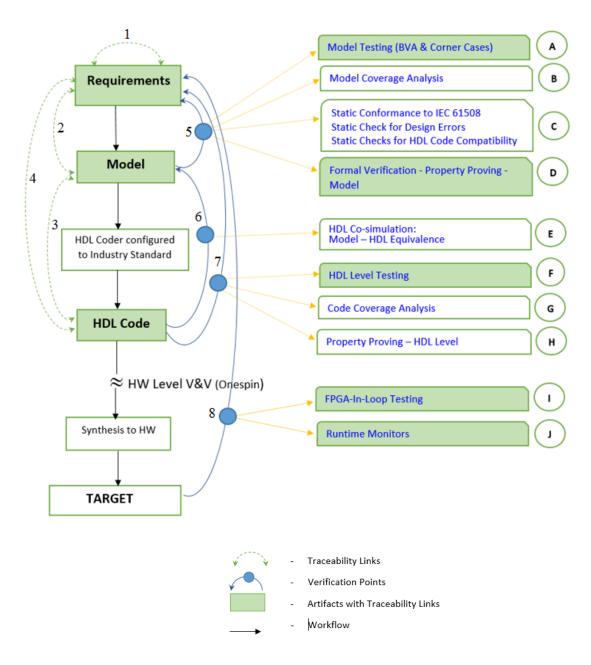

| Figure 7: V&V Workflow for SymPLe architecture                                                         | 40  |

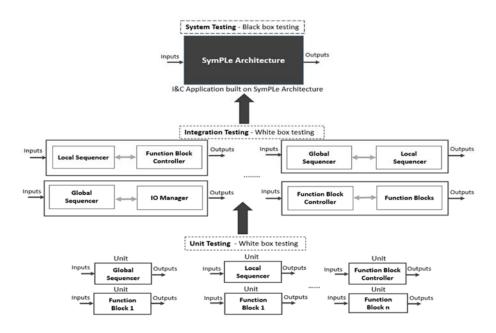

| Figure 8: Model Testing Hierarchy as applied to SymPLe architecture                                    | 46  |

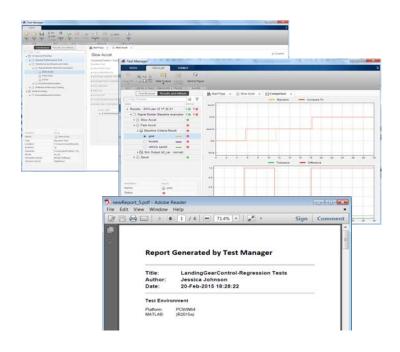

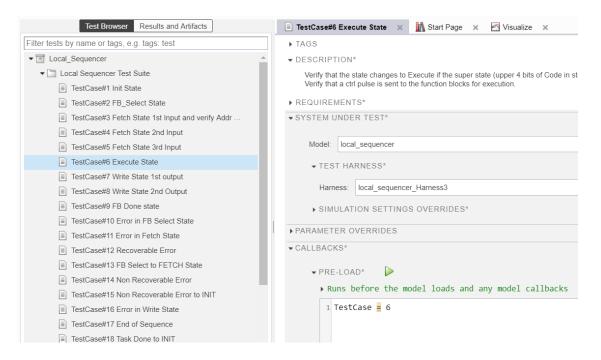

| Figure 9 : Test Manager Interface [54]                                                                 | 47  |

| Figure 10: Graphical representation of test assessment results and design signals in Test Manager      | 47  |

| Figure 11: Test Harness and Design Model interaction [54]                                              |     |

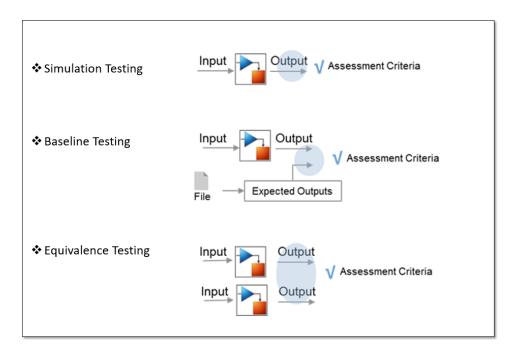

| Figure 12: Simulation, Baseline and Equivalence Testing on Models [54]                                 | 50  |

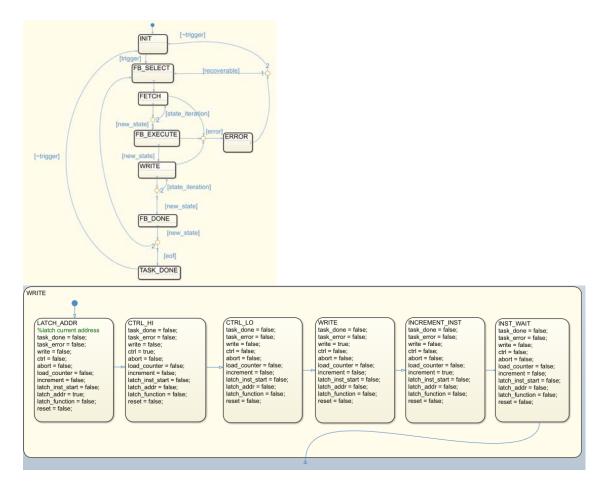

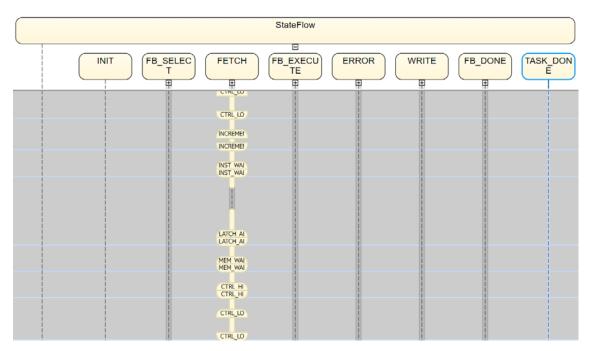

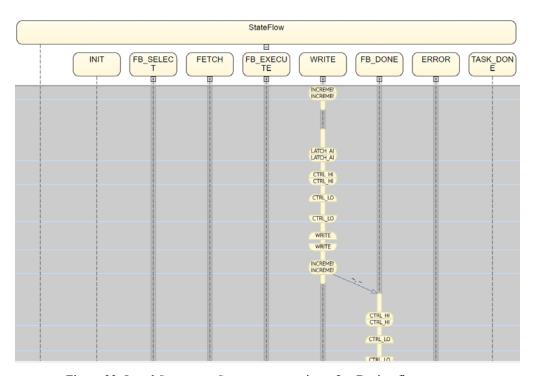

| Figure 13: Local Sequencer Top level State Machine and sub-states in WRITE state                       | 52  |

| Figure 14: Assigning TestCase parameter value in each Testcase in Test Manager                         | 53  |

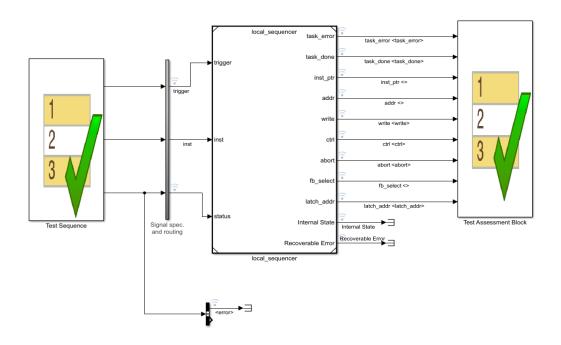

| Figure 15: Local Sequencer Test Harness                                                                | 54  |

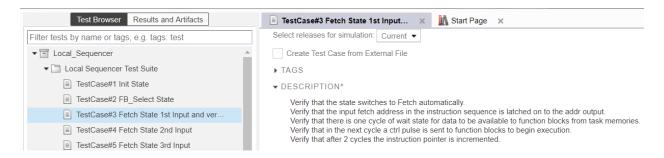

| Figure 16: Test Case Description in Test Manager                                                       | 54  |

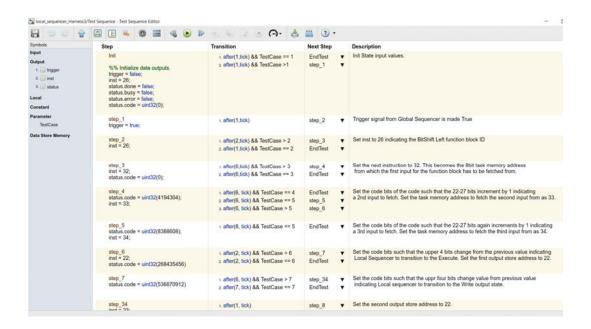

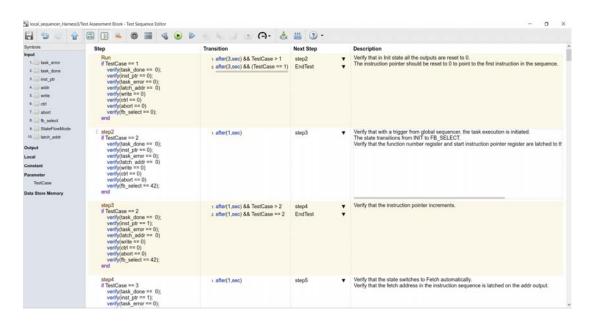

| Figure 17: Test Input Sequences in the Test Sequence Block                                             | 55  |

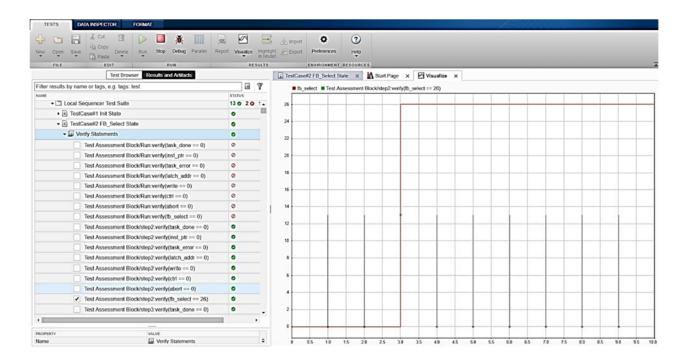

| Figure 18: Verify statements in Test Assessment Block                                                  | 55  |

| Figure 19: Feeding Test Inputs and Expected Outputs in an Array format within the M script             | 57  |

| Figure 20: Test Results generated by M Script - Inputs, Expected & Actual outputs for testcases in     |     |

| Tabular format                                                                                         | 58  |

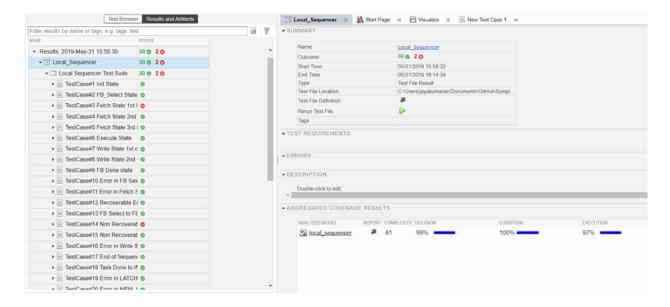

| Figure 21: Test Results Summary in Test Manager                                                        | 58  |

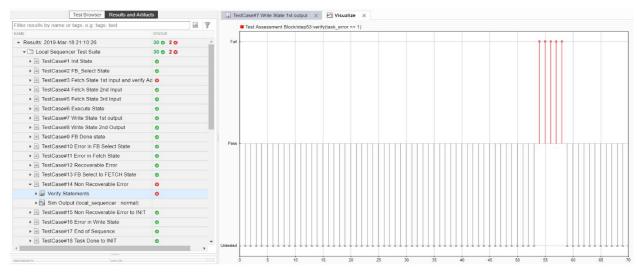

| Figure 22: Graphical plot of Verify statement results with respect to test execution time in Test Mana | ger |

|                                                                                                        | 60  |

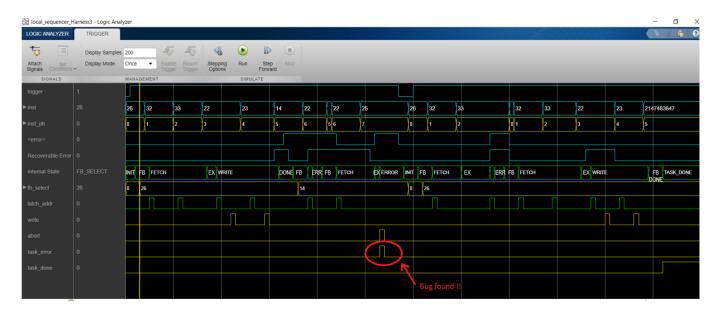

| Figure 23: Analyzing Local Sequencer input and output signals in Logic Analyzer                        | 60  |

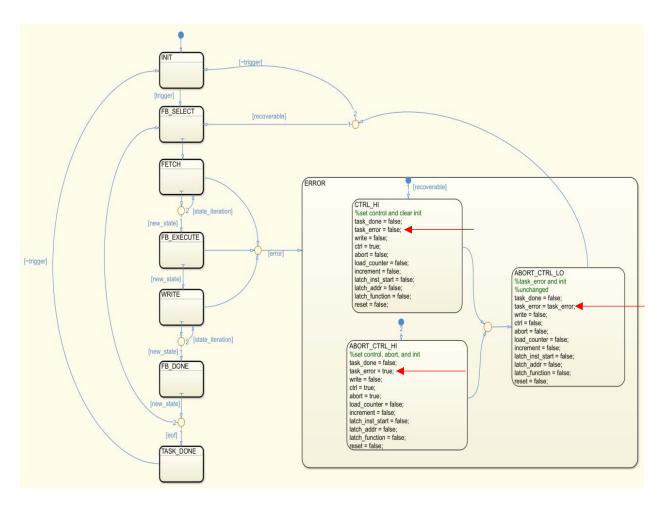

| Figure 24: ERROR State in Local Sequencer State Machine                                                | 61  |

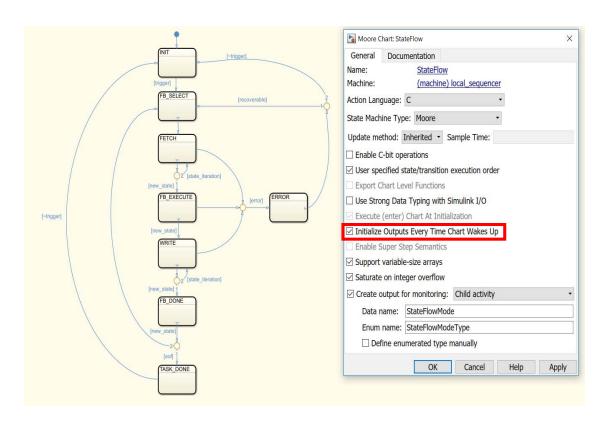

| Figure 25: Local Sequencer State Chart Settings                                                        | 62  |

| Figure 26: FB Controller Test Inputs in the Logic Analyzer and Animations in FB Controller State       |     |

| Machine                                                                                                | 64  |

| Figure 27: (i) State Sequence View with Bug in FB Controller, (ii) State Sequence View with Bug fix    | ted |

| in FB Controller                                                                                       |     |

| Figure 28: Single step execution in subtractor function block                                          | 66  |

| Figure 29: Error Codes implemented in SymPLe.                                                          |     |

| Figure 30: Datatype Error Detection                                                                    |     |

| Figure 31: Deadlock Scenario detected in Integration testing                                           |     |

| Figure 32: Integration Test Failure: Local Sequencer state sequence view                               |     |

| Figure 33: Local Sequencer State sequence view after Design fix                                        |     |

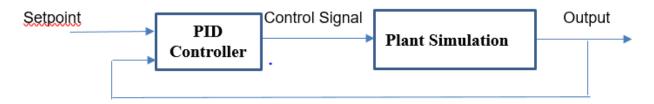

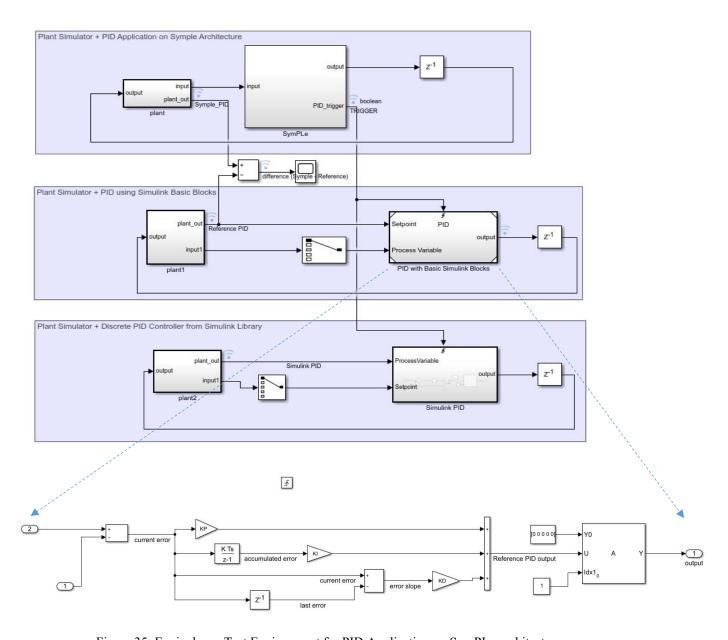

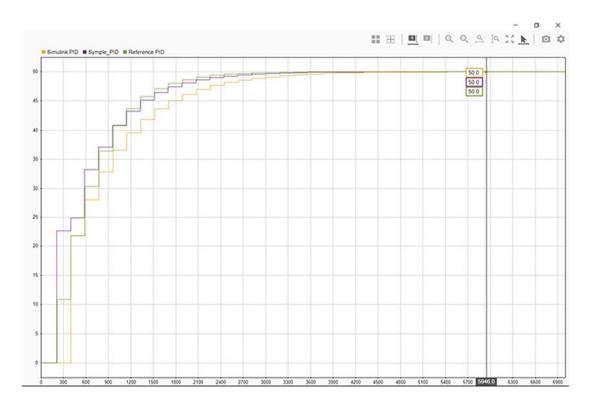

| Figure 34: PID Controller and Plant Closed Loop Test Environment.                                      |     |

| Figure 35: Equivalence Test Environment for PID Application on SymPLe architecture                     |     |

| Figure 36: Graphical plots of PID outputs from SymPLe PID and the two reference PIDs in Simulink       |     |

| Data Inspector                                                                                         |     |

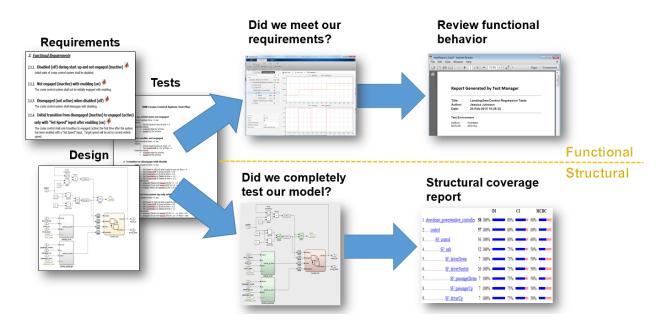

| Figure 37: Functional and Structural Coverage [54]                                                     | 73  |

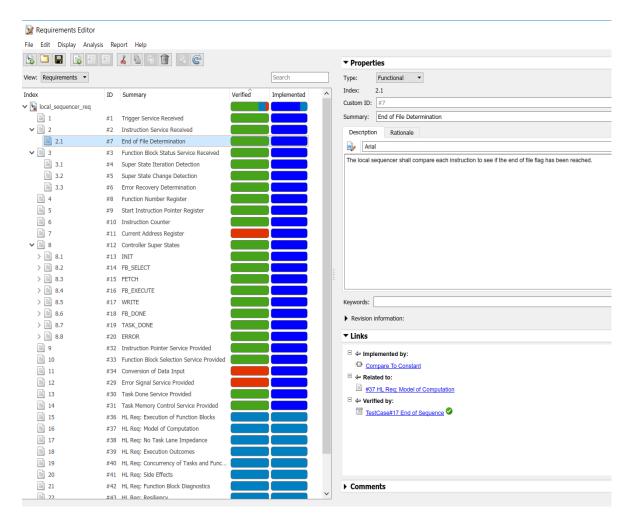

| Figure 38: Requirements Editor view showing Implementation and Verification status and Forwar  | :d      |

|------------------------------------------------------------------------------------------------|---------|

| traceability links from Requirements to testcases.                                             |         |

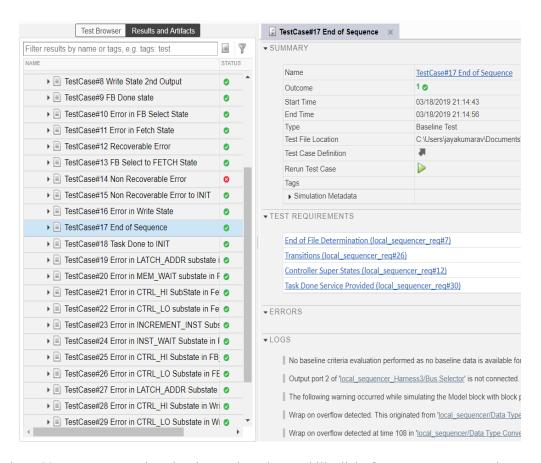

| Figure 39: Test Manager view showing Backward Traceability links from Testcases to Requireme   | ents 76 |

| Figure 40: MC/DC Coverage [54]                                                                 |         |

| Figure 41: MC/DC Coverage highlighted in the model                                             | 79      |

| Figure 42: Model Coverage Analysis summary                                                     | 80      |

| Figure 43: Low coverage due to over specified design                                           | 81      |

| Figure 44: Static analysis checks for IEC 61508 compliance                                     | 83      |

| Figure 45: Dead Logic Detected during static Design error detection on Models                  | 85      |

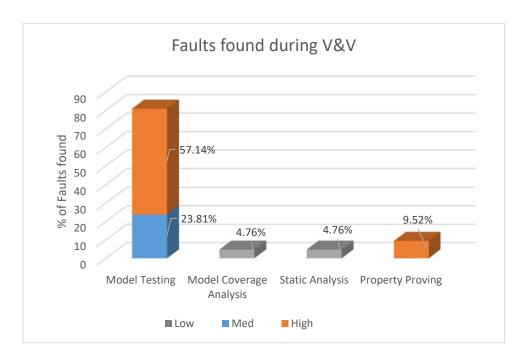

| Figure 46: Design faults found in SymPLe architecture by V&V process                           |         |

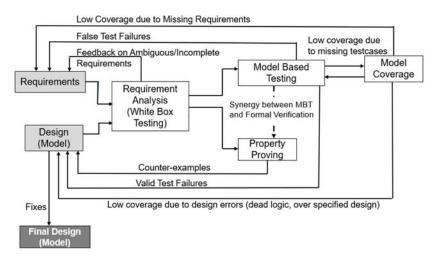

| Figure 47: Non Linear Model based verification process                                         |         |

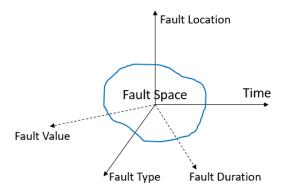

| Figure 48: Fault Space                                                                         | 94      |

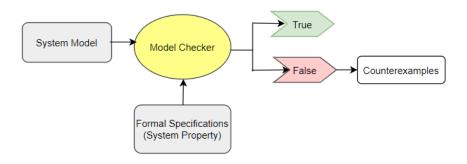

| Figure 49: Model Checking                                                                      | 98      |

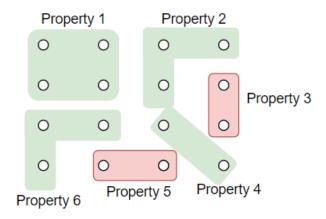

| Figure 50: Uncovered state-output space points due to missing properties                       | 101     |

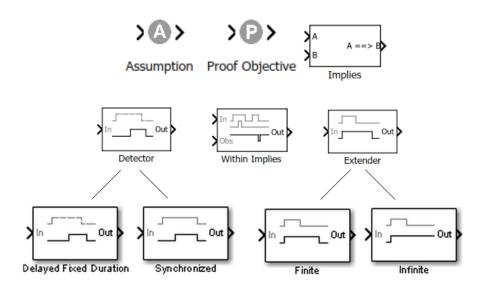

| Figure 51: Simulink Design Verifier Blocks: Proof Objectives, Constraints and Temporal Operato | rs [90] |

|                                                                                                | 103     |

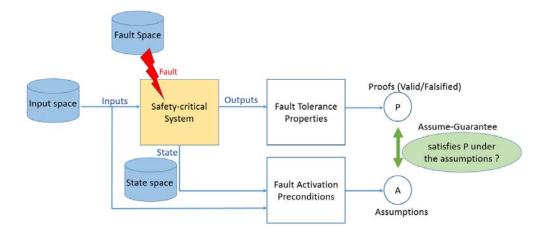

| Figure 52: Fault Injection with Property Proving                                               | 105     |

| Figure 53: Classical Fault Injection vs Property Based Fault Injection                         | 106     |

| Figure 54: Classical Fault Injection Workflow                                                  | 107     |

| Figure 55: Property Based Fault Injection Workflow                                             | 110     |

| Figure 56: Property Based fault injection - Fault-Input-State space Coverage                   | 111     |

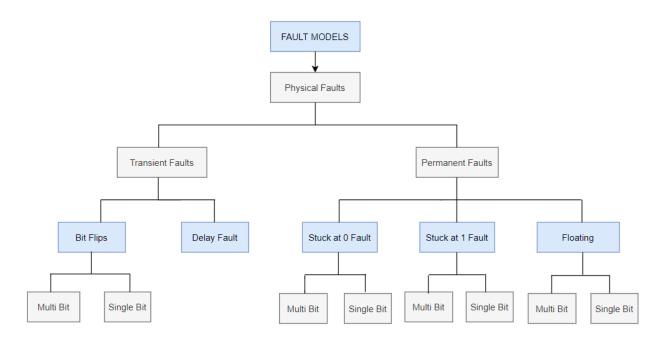

| Figure 57: Fault Model Taxonomy                                                                | 113     |

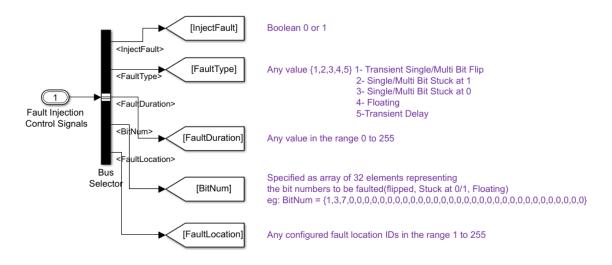

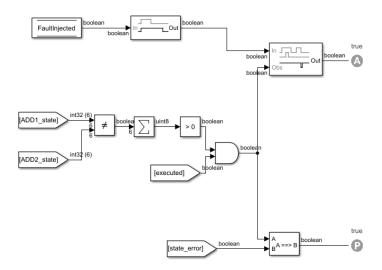

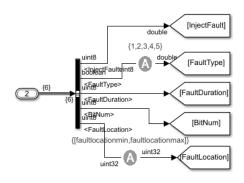

| Figure 58: Fault Injection Control Signals                                                     | 114     |

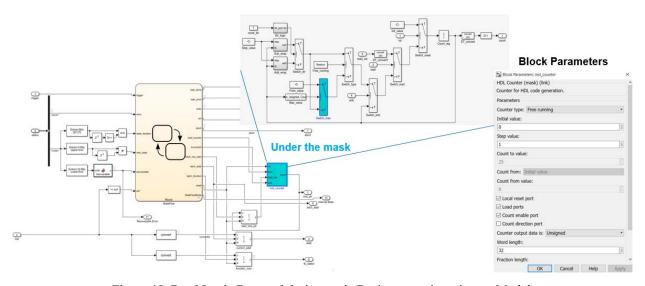

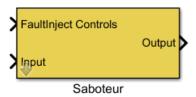

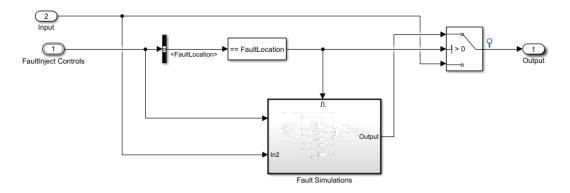

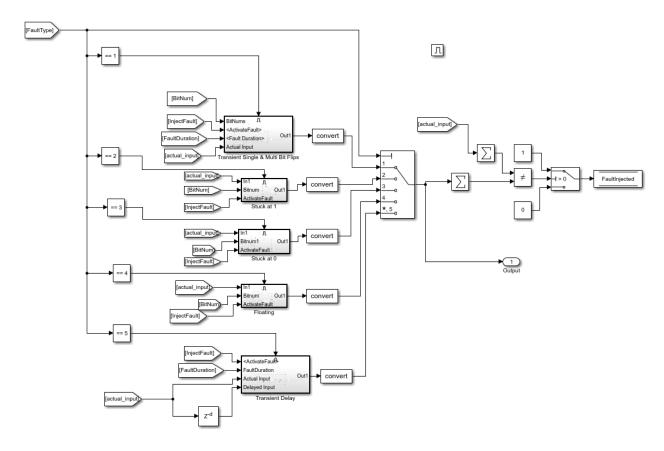

| Figure 59: Saboteur Masked Subsystem                                                           | 115     |

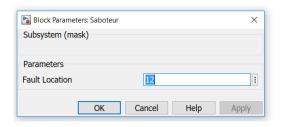

| Figure 60: Saboteur Location Parameter                                                         | 115     |

| Figure 61: Inside the Saboteur subsystem: Level 1                                              | 116     |

| Figure 62: Inside the Saboteur subsystem: Level 2                                              |         |

| Figure 63: Saboteur Inserted model                                                             | 118     |

| Figure 64: Hardware Redundancy in Function Blocks [48]                                         | 119     |

| Figure 65: Property for proving hardware redundancy of Function Blocks                         | 122     |

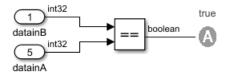

| Figure 66: Input data equivalence                                                              | 122     |

| Figure 67: Funcblock selection                                                                 | 122     |

| Figure 68: Fault Injection Control Signals                                                     | 123     |

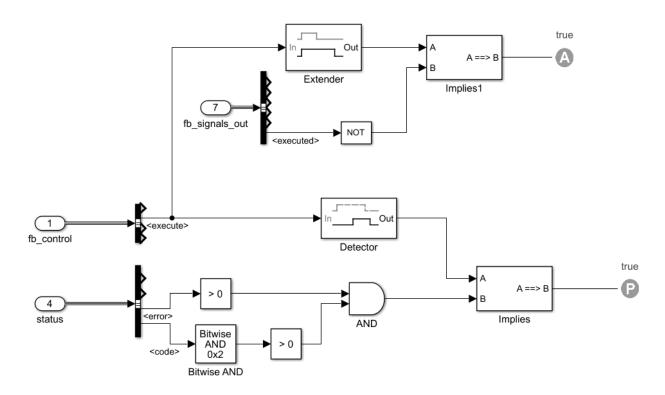

| Figure 69: Timeout Detection Feature Property                                                  | 126     |

#### **List of Tables**

| Table 1: Implemented Function Blocks in SymPLe [51]                             | 32  |

|---------------------------------------------------------------------------------|-----|

| Table 2: Table showing IEC 61508 certified Mathworks Products                   | 37  |

| Table 3: V&V workflow phases to IEC 61508 Requirements                          | 39  |

| Table 4: Faults Found during the presented Model-based Design Assurance Process | 86  |

| Table 5: Function Block Error Detection Capabilities [51]                       | 120 |

| Table 6: Function Block Fault Injection Campaign Results                        | 123 |

#### **Publications**

(Primary) Achieving Verifiable and High Integrity Instrumentation and Control Systems through Complexity Awareness and Constrained Design. No. 15-8044. Electric Power Research Institute (EPRI), 2019.

(Primary) Preliminary Results of a Bounded Exhaustive Testing Study for Software in Embedded Digital Devices in Nuclear Power Applications: Light Water Reactor Sustainability Program Idaho National Laboratory U.S. Department of Energy, Sep 2019

(Secondary) Lessons and Experiences Learned Applying Model Based Engineering to Safety Critical FPGA Designs. October 2018 Conference: 11th International Workshop on the Application of FPGAs in NPPs

#### In preparation

(1<sup>st</sup> Author) Property-Based Fault Injection: A Novel Approach to Model-Based Fault Injection for Safety Critical Systems, IMBSA 2020

(1<sup>st</sup> Author) On the Application of Systematic t-way Software Testing for Safety Critical Embedded Digital Devices in Nuclear Power

(2nd Author) Findings and experiences on applying IEC 61508 compliant model-based verification to an FPGA based system for Nuclear Industry, IMBSA 2020

(2<sup>nd</sup> Author) Design and Assessment of multilevel Runtime Verification framework using model-based engineering

(2<sup>nd</sup> Author) Design and Realization of Runtime Verification Monitors using Model-based Engineering and Event Calculus

### **List of Abbreviations**

CPS Cyber Physical Systems

MBD Model Based Design

IC Integrated Circuit

IEC International Electrotechnical Commission

FPGA Field Programmable Gate Array

IP Internet Protocol

LS Local Sequencer

GS Global Sequencer

FB Function Block

HW Hardware

SW Software

MBDE Model Based Design Engineering

DV Design Verifier

ISO International Organization for Standardization

V&V Verification & Validation

MIL Model-In-Loop

RTL Register Transfer Level

SEU Single Event Upset

HDL Hardware Description Language

VHDL Very High Speed Integrated Circuit Hardware Description Language

FI Fault Injection

LTL Linear Temporal Logic

MTL Metric Temporal Logic

FMEA Failure Mode and Effects Analysis

XML Extensible Markup Language

MC/DC Modified Condition / Decision Coverage

I&C Instrumentation & Control

PID Proportional Integral Derivative

SIL Safety Integrity Level

CLB Configurable Logic Block

UML Unified Modeling Language

FBD Function Block Diagram

PLC Programmable Logic Controller

FTA Fault Tree Analysis

STAMP System-Theoretic Accident Model and Processes

STPA Systems Theoretic Process Analysis

ABVFI Assertion Based Verification Fault Injection

BDD Binary Decision Diagrams

FIM Fault Injection Module

ASIC Application-Specific Integrated Circuit

MBT Model Based Testing

NPP Nuclear Power Plant

IO Input Output

SIHFT Software Implemented Hardware Fault Tolerance

FDIM Fault Detection, Isolation and Mitigation

SDLC Software Development Life Cycle

GUI Graphical User Interface

MBDA Model Based Design Assurance

SRAM Static Random-Access Memory

ID Identifier

NaN Not a Number

#### **Abstract**

# SYSTEMATIC MODEL-BASED DESIGN ASSURANCE AND PROPERTY-BASED FAULT INJECTION FOR SAFETY CRITICAL DIGITAL SYSTEMS

By Athira Varma Jayakumar, B.Tech.

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Engineering with a concentration in Electrical and Computer Engineering at Virginia Commonwealth University

Virginia Commonwealth University, 2020

Major Director: Dr. Carl R Elks

Associate Professor, Department of Electrical and Computer Engineering

With advances in sensing, wireless communications, computing, control, and automation technologies, we are witnessing the rapid uptake of Cyber-Physical Systems (CPS) across the spectrum, with a potential economic impact of as much as \$11.1 trillion per year by 2025 in different settings, including connected vehicles, healthcare, energy, manufacturing, smart homes, and smart cities [1]. Many of these applications are safety-critical in nature. Meaning that they depend on the correct and safe execution of software and hardware that are intrinsically subject to faults. These faults can be design faults (Software Faults, Specification faults, etc..) or physically occurring faults (hardware failures, Single event upsets, etc..) . Both types of faults must be addressed in design, development and implementation of these types of critical systems.

As such, several safety critical industries (including automotive, avionics, medical) have widely adopted Model Based Engineering and Design paradigms to address and manage the design assurance processes of these complex CPSs. This thesis studies the application of IEC 61508<sup>1</sup> compliant model based design

<sup>&</sup>lt;sup>1</sup> IEC 61508 "Functional Safety of Electrical/Electronic/Programmable Electronic Safety-related Systems (E/E/PE, or E/E/PES)", is a basic functional safety standard applicable to all kinds of industry. It defines functional safety as: "part of the overall safety relating to the Equipment Under Control.

assurance methodology on a representative safety critical digital architecture targeted for the Nuclear power generation facilities. The study presents detailed experiences and results to demonstrate the benefits of Model testing in finding design flaws and its relevance to the subsequent verification steps in the workflow.

This thesis extends the model based design assurance workflow in part 1 to include 'model based fault injection based on property proving', to study the response of the system to injected faults. To address the impact of physical faults on the digital architecture we develop a novel property based fault injection method which overcomes some of the deficiencies of traditional fault injection methods. The model based fault injection approach presented here is novel in terms of the high efficiency and input/state/fault space exhaustiveness achieved, by utilizing formal verification principles to identify fault activation conditions and prove the fault tolerance features. The fault injection framework facilitates automated integration of fault saboteurs throughout the model to enable exhaustive fault location coverage in the model. The property based fault injection technique we developed has not been reported in the literature to date.

# **Chapter 1 Introduction**

#### 1.1 Motivation

We are witnessing the rapid uptake of Cyber-Physical Systems (CPS) technology across the spectrum, with a potential to impact society in ways that could not be envisioned 15 years ago. It is estimated the economic impact of such technology could be as much as \$11.1 trillion per year by 2025[1]. Cyber-physical systems (CPS) integrate a diverse set of hardware and software components to provide new service capabilities of which some could be of a critical nature. Technologies that enable the realization of CPSs include embedded computing platforms, System on Chip, smart sensors and actuators, IP based software, and wireless communication networks. Examples of their everyday use include energy operation centers, wearable devices, connected healthcare, diver-assisted automobiles, military coordinated operations and homeland security monitoring centers, to name a few. As CPS technology evolves and matures, we, as a society will depend on them more and more for critical services – 911 call centers, water supply and distribution, air space management, etc.

A system is deemed *critical* if the services the system provides to its end-users or environment are important for the end-users or environment to function normally. A system is *safety critical* if the loss of service can lead to hazards that affect the safety of the end-users or the environment. Hazards are the precursors to accidents, outages, catastrophes that include loss of life, damage to the environment and infrastructure. Examples of safety critical systems include commercial aircraft, medical therapy and diagnosing equipment, autonomous driving systems, and nuclear reactor protection systems – among many.

Very often these systems must provide uninterrupted operation to supply critical service even in the presence of faults or become fail-safe until failures are repaired. Redundancy and fault tolerance strategies are used to cope with randomly occurring physical faults and failures [2]. However, faults that arise from design oversights, software coding mistakes or inadequate requirements are called *systemic failures* that can lead to *common cause failures*. Meaning, their unintentional activation can result in complete failure of the system and thus defeat any redundancy and safeguards mechanisms. As an example, in 2014 a 911 regional emergency call routing center in Colorado failed in way that prevented 911 emergency calls to route to their destination. The root cause of the problem was traced to a specification/software flaw responsible for assigning the route codes. The software maxed out at a pre-set

limit; the software literally stopped counting at 40 million calls. As a result, the routing system stopped accepting new calls, leading to a series of cascading failures across 8 states in the 911 infrastructure. For reasons and circumstances like this, detecting and removing systemic design faults are of particular concern in the research community of safety critical systems [3].

#### 1.2 Complexity in Software Based Systems

Computer hardware and its software in the context of critical computing are sometimes called an *embedded computer or device*. An embedded digital device in a car, for example, can be the software (SW) controlled gearbox or an anti-locking brake system computer; that has a function within the overall system – the car. Software controlled embedded devices like microprocessors do not; however, behave like usual physical machine elements. The microprocessor is a general purpose device that when given a program to execute, in effect becomes the machine it is designed (programmed) to be. Simply explained, using a microprocessor we no longer need to build intricate mechanical or analog devices to control, for example, a gearbox controller. We simply need to write down the design of the controller using SW instructions to accomplish the intended goal. These instructions are then made available to the microprocessor which, while executing the instructions, in effect becomes the controller. The immense flexibility of computers and their ability to perform complex tasks efficiently, have led to a great increase in their use, even into critical systems where the consequence of failure could be significant. This immense flexibility has a downside - complexity naturally arises. Complexity of software and hardware design is one of the primary sources of design flaws that can lead to serious system failures in safety critical systems.

As we have observed in recent cases, highly integrated systems can be susceptible to cascading failures leading to accident consequences [4]. The root causes of these failures are very often traced back to design flaws where poorly understood interdependencies between computer control systems and automation result in incorrect and unsafe actions [5]. As complexity increases, design faults are more prone to occur when more interactions make it harder to identify hazard behaviors through traditional software and system testing methods [6]. For these reasons, more powerful design assurance methods and models that capture these complex interactions with assumptions and interactions are much needed at this time.

#### 1.3 Early Detection of Systematic Failures

The critical nature of CPSs requires thorough and effective analysis throughout their lifecycle but especially at the early design development phase. This is supported by several studies where it is estimated that 70-80% of the decisions affecting safety and security are made in the early concept development phase of any project [7] [8]. Figure 1 illustrates the importance of detecting and removing systematic design errors. First, early identification of a design flaw in the lifecycle significantly reduces the cost of remediation ("fixing" the bug) as compared to late lifecycle detection. Secondly, detecting a design flaw early in the lifecycle process removes the risk that the design flaw leads to hazard and endanger lives. Early systematic detection, analysis and mitigation of design flaws are part of the growing technical body of research called Design Assurance Methodologies and Testing.

Figure 1: Decision Effectiveness during life cycle (adapted from [9])

#### 1.4 The Role of Standards

With critical embedded systems being increasingly used in society, the safety of the products becomes extremely important as the consequence of failure can cause harm to life and/or environment. Consequently, safety critical systems industries are regulatory and standards driven – meaning products are required to comply with standards and guidelines. Each industry has a unique set of governing safety standards for product software and system development. As example, IEC 61508 is the general International functional safety standard for Electronic/Programmable Electronic Safety related systems.

ISO 26262 is the functional safety standard for automotive, EN 50128 for Railways, IEC 62304 for Medical devices and DO-178B for Airborne Systems. For achieving certification on these safety standards, the product design needs to demonstrate the management of both random and systematic failures of the product. In addition to that, there should be evidences to show that product development follows proven and recommended failure risk reduction processes.

A standard of particular interest to this research is IEC 61508. This standard is important for several reasons; (1) because it is like a "mother" standard, as many other safety critical system standards like ISO 26262, DO-178B, DO-254, IEC 61513 (nuclear 61508) are heavily influenced by 61508-3; (2) its recent consideration by US Nuclear Regulatory Commission and its longtime acceptance by the international nuclear energy community. Additionally, IEC 61508-3 provides guidance on both software and hardware aspects of design assurance which is important for a HW and SW based design.

IEC 61508 defines various levels of Safety Integrity Levels (SIL) for systems with SIL level 4 being considered highest dependable system and SIL level 1 being considered the least. IEC 61508-3 defines the guidelines and processes to be followed at each stage of the software development including requirements, design and verification. IEC 61508 specifies several *normative requirements* that influence the choice of design assurance workflow and tools. These include V model, Bi-directional traceability and use of Formal and Semi formal methods. Forward and backward traceability between all levels of artifacts ranging from requirements, design, code and verification is a mandatory requirement for SIL levels 3 and 4 in IEC 61508. IEC 61508 recommends the usage of "V model" to represent the software development lifecycle. A more detailed discourse on IEC-61508 can be found at [10].

#### 1.5 Summary

Engineering history has revealed that design faults are major causes of catastrophic failures, from the Tacoma Narrows Bridge collapse to the Boeing 737 MCAS accidents [11]. Survey on failure sources of traditional fault tolerant and non-fault tolerant computing systems have found that almost 75% of system failures originated from flaws in early design phase activities that are eventually propagated to software and hardware implementation.[12] With design faults being a bottleneck of systems dependability, effective and comprehensive methods need to be employed during the specification and design and verification of safety critical systems. At this time, there are numerous approaches and methodologies being proffered [13]. This thesis examines two aspects of design assurance for safety critical CPSs; (1) the feasibility, benefits and challenges of using IEC 61508 standard from a *model-based verification*

perspective, and (2) the development and application of a novel fault injection technique that overcomes problems with traditional fault injection. Specifically, we addresses the physical faults problem by building a model-based fault injection framework based on property proving to analyze the impact of physical faults on system models and verify the fault tolerance features very early in the design phase. The overall goal of this thesis is to investigate, develop, and collect credible evidence on the efficacy of model based design assurance in the context of IEC 61508. A farther contribution of this thesis is the novelty of developing model based design assurance workflows for FPGA based systems which have not been widely reported in the literature.

#### 1.6 Outline

This thesis is organized as follows. Chapter 2 gives background information on this research work; discusses dependability concepts and safety critical systems principles, and states the contributions of this thesis. Chapter 3 highlights related work in the field of model based design assurance and fault injection. Chapter 4 gives brief overview of the architecture and components of the representative system that is subjected to this experimental study on model based design assurance. Initial part of chapter 5 describes the basic concepts of Model based engineering and the selection of MBD tools. Further, the chapter presents the model based design assurance workflow developed for IEC 61508 compliance and describes the Model testing phase and experimental results in detail. Chapter 6 talks about the model coverage analysis phase and the implications of low model coverage. Chapter 7 provides details on the static analysis phase in the presented V&V workflow. Chapter 8 summarizes the findings and lessons learned during the application of the Model based design assurance process. Chapter 9 discusses the proposed approach of property-based fault injection at the model-level and presents the experimental results. Finally, Chapter 10 gives the Conclusions and Future work.

# **Chapter 2 Background**

This chapter gives an overview of dependability concepts to place the work in context. It also introduces common definitions, terms, and relationships that are a part of dependability theory. The later part of this chapter gives a brief background on fault injection, its importance to design assurance and finally the major contributions of this work.

#### 2.1 Concepts of Dependability

Dependable systems concepts and technology have evolved over the past 40 years from a large community of researchers and practitioners. A significant contribution to dependability concepts and theory is the work by Avizienis, Laprie, and Randell [14]. This work is widely recognized as a standard for understanding the concepts of critical system attributes. This thesis adopts [14] concepts of dependability to provide consistent terminology when discussing faults, errors, and failures with respect to safety critical systems. For a more in depth review of dependability concepts, [14] paper provides a detailed appreciation of the topic. We say *dependable system* has the ability to provide its intended, expected and agreed upon functions, behavior, and operations in a correct timely manner [14].

In dependability theory, a *system* is defined as an interconnected set of elements that is <u>coherently</u> organized in a way that achieves objective or purpose. These elements can be other systems, components, including hardware, software, humans, and the physical environment. The border between the system and its environment is the *system boundary or common interface*. The *service* delivered by a system is its behavior as it is perceived by its user(s) – which could be other systems, humans, and physical control. [15]

V

The common definition of *Dependability* is "Dependability is the ability of a system to deliver service that can justifiably be trusted"[14]. Another alternate definition of dependability is, "Dependability is the ability of a system to operate in such a way that the frequency and severity of the service failures happening are acceptable to the user."[14]. The second is more accepted than the first.

The *attributes* of dependable systems are the primary means by which the quantitative and qualitative requirements of a system are specified. Figure 2 shows the taxonomy of dependability attributes. The following are some basic terms and concepts related to dependable system attributes:

**Definition 1**: *Reliability*, a conditional probability that the system will perform correctly throughout the interval [t0, t], given the system was performing correctly at time t0 [2], which is related to the continuity of service.

**Definition 2**: Availability, a probability that a system is operating correctly and is available to perform its functions at the instant time, t [2], which is related to readiness for usage.

**Definition 3**: *Safety*, a probability that a system will either perform its functions correctly or will discontinue its functions in a manner that does not disrupt the operation of other systems or compromise the safety of any people associated with the system [2], which is related to the non-occurrence of catastrophic consequences on the environment.

**Definition 4**: *Integrity*: absence of improper system alterations [2].

Figure 2: Taxonomy of Dependability[14]

#### 2.2 Impairments or Threats to Dependability

Faults, errors, and failures affect the ability of a system to deliver its dependability attributes (e.g., safety, reliability, performance, etc.). Hence, they are called the *impairments* or *threats* of dependability. Correct service is delivered when the service accurately reflects the system function. A *service failure*, abbreviated here to *failure*, is an event that occurs when the delivered service deviates from correct service. A failure is either because the service does not comply with the functional specification, or because this specification did not adequately describe the system function. A failure is a transition from

correct service to incorrect service (i.e., not implementing the system function). The deviation from correct service may assume different forms that are called failure modes.

In digital systems, delivered service is dependent on sequence of execution states, a service failure means that at least one (or more) states of the system deviates from the correct service state. This deviation is called an *error*. Error propagation occurs when an error is successively transformed into other errors through execution of instructions, program states, and functions on a digital system, (e.g., errors from function A propagate to function B when it receives information from component A).

The cause of an error is called a *fault*. Faults can be internal or external to a system. Given a fault is present in a system, the fault turns active when it manifests into an *error*; otherwise, it is latent. Fault activation occurs when various activation factors align to initiate the dormant fault – these include inputs, modes of operation, program execution, etc.

Implicit in the definitions of the above terms is a cause-effect relationship. The well-known 3-universe model depicted in Figure 3 shows the relationship between faults, errors, and failures [2]. Faults cause errors, and errors may propagate to the system interface to cause service failures.

Figure 3: Three Universe Model [2]

The physical universe depicts where faults can originate. *Operational faults* are associated with the *use* phase of the system. During the *use* phase, the system interacts with its environment and may be adversely affected by faults originating in it. These types of faults include a wide variety of faults. Such as:

• Faults from naturally occurring phenomena – HW faults, semiconductor faults, power faults, connector faults, etc.

- Faults introduced from improper operator use improper commands, improper configuration, omission faults, etc.

- Faults introduced from malicious intruders cyber-attacks, theft of information, exploitation, etc.

Design faults occur in the development phase of the system. The development phase includes all activities from requirements to testing to implementation to deployment. During the development phase, the system design process successively refines the system from requirements and specification to hardware and software implementations. During the development process, design and development faults may be introduced.

Design faults can arise from a number of sources. A few are;

- Fault arising from mistakes misinterpretations of requirements, ambiguity in specification language, improper implementation of design, etc.

- Faults arising from omissions Requirements that were overlooked, incomplete requirements or specifications, assumptions not stated, functionality left out of implementations, etc.

- Faults arising from improper commission Requirement that is not needed, Functionality that is present but not needed for the application, redundant functionality, dead logic, implementation has functionality that was not intended, etc.

Physical faults on the other hand are faults that occur due to adverse physical phenomena [16] and affect the operation of the system, although the design of the system could be flawless. Manufacturing defects or hardware damages like permanent open or short circuits that cause the electronic component to stop functioning or function incorrectly are examples of Physical faults. Cracking and critical failure of the semiconductor devices happening as a result of electrical, thermal or mechanical stress beyond the device's maximum ratings could be causes of permanent physical faults. Power fluctuations, switching transients, soft errors arising due to electromagnetic interferences and cosmic radiations are other major reasons for transient physical faults. Single or multi event upset is the change in state of memory or logic elements in a micro electronic device when they are struck by high energy charged particles. They are classified as soft errors as they are non-destructive and get fixed when the flipped bits get back to the previous state. [17] Alpha particles which are essentially particles identical to a helium-4 nucleus released from thorium and uranium impurities in the packing material of the device are one of the sources of the soft errors [18]. Cosmic rays which are a major source of soft errors, highly threatening to the aerial

devices, are high energy particles originating in space. The cosmic rays when entering the earth's atmosphere causes a series of cascaded particle showers thereby generating high speed neutrons. The alpha particles and neutrons when passing through the layers of semiconductor device material are capable enough to create an ionization path with free electrons and holes causing change of state of storage elements within the device. [19] Another category of transient physical faults is the delay fault. Delay faults represent faults that arise due to propagation and transition delays at the gate level during power supply disturbances and single event transients. Delay faults at a component in the hardware do not make the component logically incorrect, but instead delays its response causing a timing error. Another set of physical faults are intermittent faults that appears at irregular intervals possibly due to a loose connection in the circuit or unstable hardware and software states or intermittent power transients.

Interaction faults are the class of faults that occur due to faults in the human – machine interactions. These normally happen when right procedures and good practices are not followed during the operation or maintenance of the devices. They could be accidental or deliberate and of malicious or non-malicious intent. As interaction faults are human-made faults, they are usually not considered when studying system centric faults as in other studies [16]. The same approach is taken in this work by addressing only the design and physical faults in the fault space.

#### 2.3 Important Principles for Safety Critical Systems

In the context of safety critical systems, the goal is to preserve safety. Accordingly, failures associated with digital systems that lead to hazardous conditions must be extremely improbable<sup>2</sup>. Digital systems without any additional protection against failures are most likely to fail in ways that are unacceptable to the overall safety of the system. Thus, a defensive fault tolerant strategy must be employed to do one or two actions upon the occurrence of erroneous behavior associated with the digital system. These are:

1 **A fail-safe action**: Upon detection of an error that could lead to failure, *force* (by some defensive measure) the digital system to discontinue its operation in manner that does not compromise the safety requirements of the overall system [20].

<sup>&</sup>lt;sup>2</sup> The term "extremely improbable" is dependent on the application requirements which vary from application to application. For example, the requirement for digital flight control systems in civilian air transports is 10-9 failures per 10 hour flight—which is extremely improbable.

2 **A fail-operational action:** Upon detection of error that could lead to failure, *overcome* (by some corrective action) the erroneous condition such that the operation of the digital system is able to continue according to its specified safety and functional requirements [20].

Fail-safe and fail-operational actions are principle goals for safety critical systems. These actions are not inherent in most digital systems; the system must be designed to behave as a fail-safe or fail-operational system. Traditionally, fault detection and/or fault tolerance mechanisms are added to the fault intolerant design to detect and possibly correct the effects of faults during the operation of the system. There are four main approaches as described by [14] that are a *means* to realize more dependable components:

- 1 **Fault avoidance** means to prevent the occurrence or introduction of faults. How to avoid faults by design, i.e., try to build the system correctly from the beginning.

- 2 **Fault tolerance** means to avoid service failures in the presence of faults.

- Fault removal means to reduce the number and severity of faults. How to reduce; by testing and verification to find the presence of faults

- 4 **Fault forecasting** means to estimate the present number, the future incidence, and the likely consequences of faults.

This thesis is focused on methods related to fault avoidance, fault removal, and testing fault tolerance mechanisms via fault injection.

#### 2.4 Fault Avoidance and Fault Tolerance Concepts

Fault avoidance refers to methods and practices used for producing a system or component that are, by design, free of design flaws to as "low as reasonably practicable". Fault avoidance strives to prevent faults from being introduced into the systems by; (1) applying rigorous design and specification processes, and/or (2) taking necessary quality control measures during the design, implementation, and manufacturing of the system. As stated earlier, design faults are one of the major causes of failures in digital systems (and software intensive systems). Examples of fault avoidance methods are following safe programming practices, performing rigorous coverage based SW testing [21], formal specification and verification [22] and extensive reviews on the system. Quality control during manufacturing involves selection of defect free components, strong production process disciplines and quality inspection checks of products. While design faults can be avoided using rigorous design and verification process, physical faults that occur randomly during the operation of the system can be only handled with well-formed fault detection and handling techniques for the system.

While fault avoidance is a process-oriented concept, *fault tolerance* is a product-oriented concept. Fault tolerance can be defined as the "property of a system to detect the presence of malfunctioning resources, or faults within or external to the system and continue to operate normally"[23]. Fault tolerance almost always involves the use of redundancy either at the system, hardware and software level to detect and overcome the effects of faults and thereby prevent system failures. A good introduction and detailed discourse on fault tolerance techniques can be found in [23] [24].

#### 2.5 Fault Injection

In order to study the effect of physical faults on systems, the technique of fault injection was introduced in the early 1970s. Fault injection is used to verify the fault tolerance capabilities of a system by deliberately injecting faults into the system. The types of faults injected into the system depend on the fault model used. A *fault model* is a representation that captures the behavioral and temporal aspects of faults the system is expected to experience in its operational life. The physical faults listed in the impairments and threats section of these are often studied to produce a representative fault model. The fault model is then used with fault injection techniques to inject the faults into the target system. There are a wide variety of fault injection techniques with advantages and disadvantages with respect to properties like reachability, controllability, repeatability, intrusiveness and observability. Several references provide excellent comparative overview of various fault injection techniques [25], [26].

At the broadest stance, fault injection can be broken down into three types: Physical hardware fault injection, Software based fault injection, and Simulation based fault injection.

Hardware Fault injection is a physical fault injection technique in which the faults are directly injected into an IC or device. The hardware injection could be with or without direct contact to the target hardware. Probing the pins on the target hardware is one of the easiest hardware fault injection by which the current or voltage at the pins are varied thereby causing a stuck at high or stuck at GND fault. Bridging faults are induced by connecting the probe across two or more pins. Fault injection without contact is used to inject single bit and multi bit upsets by exposing the target hardware to high energy ions radiations or electromagnetic fields. This method provides a high level of accessibility to corrupt storage elements in parts of the circuit which may be elusive by other means.

In Software fault injection, faults are induced within the software through instrumented fault injection software. The basic idea of Software fault injection is to corrupt memory and register location of the processor to emulate bit flip faults and transient faults. In practice two types of Software fault injection are often used: Software Implemented Fault Injection (SWIFI), and Compile time fault injection. SWIFI is a runtime fault injection method where a special interrupt service routines are used to "momentarily" halt the execution of code, and insert corruptions into memory and register spaces. This allows injecting faults in all levels of software including application, software driver code and operating systems. On the other hand, compile time fault injection is where different faults are inserted into the source code, compiled and executed on the target processor. Compile time fault injection can be compared to mutation testing where the target software instructions are altered to change the behavior of software thereby simulating either a physical fault or a software fault.

Simulation Based Fault injection often uses a high fidelity model of the system and simulates the code running on the model. This technique can inject fault onto a hardware or software simulation of the system model instead of directly injecting them on the actual prototype. This gives a lot of advantage, the main being that it helps in performing system failure analysis at an earlier stage in the development process. Examples of simulation tools to support simulation based fault injection are OVPsim, Simics and QEMU [27] [28]. Hardware simulations could be a VHDL or Verilog representation of the system as well. One approach to simulated FI is with the simulation model modification. With fault injection modules called *saboteurs* being inserted in the signals to be tested, the tester is able to control the activation and duration of the fault precisely and the effect the fault can be monitored on external outputs as well as on the internal signals. A second approach to simulated FI is through simulator commands where *built in* simulator commands are used to modify signal and variable values.[29]

Most fault injection methods are applied at latter stages of lifecycle development where hardware and software implementation are generally mature. The disadvantage to applying fault injection at latter lifecycle phases is twofold: Cost of changing the design to fix problems, and coverage of the fault injection. In keeping with the themes of this thesis, our interest is to explore fault injection concepts and methods that can be applied before code and hardware is developed – the so called *functional model level*. The ability to perform early systematic fault injection and propagate the results of the fault injection results into latter design decision phases can have a significant impact on design assurance.

#### 2.6 Contributions

The first part of this research work is focused on systematic development and application of fault avoidance and fault removal methods with respect to safety critical systems, specifically model based design assurance and testing methods. This thesis addresses the challenges of uncovering design faults of a digital architecture by applying model based design and verification principles in a strict IEC 61508 context. The representative system considered for this study is targeted for SIL level 3 and 4 – the most stringent in safety applications. Our approach investigates design assurance with rigorous model testing, formal verification of critical system properties using property proving and static analysis to find design faults and IEC 61508 compliance issues.

The second phase is aimed at accessing *fault tolerance* performance of the representative system due to the impact of physical faults on the system through an innovative fault injection method. A novel methodology called *property based fault injection* is introduced that provides an exhaustive coverage of the fault, input and state space of system components - with respect to fault tolerance and safety properties.

#### The contributions of this work are:

- Formulation, development and evaluation of a comprehensive end to end design assurance workflow

that spans from model to code to the hardware implementation, to support IEC 61508 safety standard.

- Gathered evidence for demonstrating the effectiveness and capacity of Model Testing and model coverage methodology to find a diverse set of design flaws.

- Formulated and developed a highly efficient concept of Property Based fault injection at the model level that is more effective and productive with respect to traditional fault injection in its completeness of input, state and fault space coverage.

- Developed and implemented a fault injection framework that facilitates automated fault injection to enable high coverage fault injection in system models.

### **Chapter 3 Related Work**

This chapter highlights several previous research and work on the Model-based design assurance and V&V activities aimed at achieving a high level of dependability for products in safety critical industries. It also presents related work in the literature on model-based or formal methods based fault injection techniques.

There has been several surveys about current state-of-the practice in the use and the assessment of Model based engineering in several industry domains, like in space and aeronautics [30] and in general embedded systems [31]. Murugesan et al in [32] presents a study on the application of model-based design and verification to medical device software development. The work describes the use of Simulink for describing continuous time control system models, Stateflow FSMs to model the mode logic behavior and Architecture Analysis and Description Language to represent the architectural models for a medical CPS. The authors also describe about the Assume guarantee approach used to verify if the architecture meets requirements and formal verification using Design Verifier to verify if the detailed behavioral model meets safety properties. Bhatt et al in [33] describes the lessons learnt and challenges faced during the adaptation of Model based design and assurance to avionics applications for compliance to DO-178B standard. The authors give an interesting comparison of the traditional vs MBD design assurance environments. Bringmann and Kramer in [34] studied the challenges involved in model based testing and introduces a new approach of MBT called the Time Partition Testing which can graphically represent test models for complex and closed loop real time environments in automotive domain. Beine's paper [35] gives a reference workflow for model based development of safety critical systems in order to achieve highest safety integrity levels as per IEC 61508 or ISO 26262 standards. The author discusses the contribution of a detailed workflow in achieving safety certification of the software tools using example of Targetlink code generation tool. Mathworks papers [36] and [37] describes the IEC 61508 and ISO 26262 compliant V&V workflows in the context of Mathworks Simulink toolchain. Marrone et al in [38] presents an approach to automatically generate formal models and test cases from high level models of the system that contain all the information necessary to the V&V purposes. This paper introduces a Model-based process driven by UML profiles and model transformations that map structural and behavioral UML diagrams to formal models and applied onto a railway control system. It also describes a software architecture supporting testing and verification activities. The study [39] proposes an efficient technique for verification and validation of automotive software in the context of ISO-26262 compliance by applying fault injection techniques combined with mutation testing approach at the model level. The

improvements include such aspects as identification of safety related defects early in the development process thus providing enough time to remove the defects.

In addition to the popularity of MBD gained in automotive, aerospace and industrial equipment industries nuclear industry has also started showing interest towards application of MBD assurance for safety critical applications. The use of the Simulation Validation Test Tool SIVAT for validating the safety critical software in Areva Teleperm TXS I&C system at the Occonee NPP [40] was one of the first model based verification attempts for nuclear energy I&C. There are several model based design verification tools used in different industries. One such tool for the Nuclear industry applications is the Nude 2.0 developed by Konkuk University and KAERI. Nude 2.0 [41] is a model based system development environment that provides automatic code generation (C, FBD, Verilog, VHDL), verification and safety analysis environment for PLC/FPGA based safety-critical digital I&Cs. It offers support for verification techniques like simulation, model-checking, equivalence checking and safety analysis techniques like STAMP/STPA and FTA.

There are several surveys [26] [42] [43] that study the state-of-art techniques in different categories of conventional fault injection - hardware-based, software-based, simulation-based and emulation-based approaches. In the last decade, FI community has started gaining interest on the application of formal methods to fault injection and to the analysis of fault tolerance mechanisms. Few works that extend formal verification techniques like model checking, assertion based verification and symbolic analysis to fault injection are discussed below.

Scott et al [44] presents a methodology called ABVFI which is fault injection based on assertion based verification. ABV is a formal verification method that checks for critical properties at the hardware level by embedding assertion statements into the hardware design (RTL). ABVFI proves selected properties of the system in the presence of faults. The fault space for this model checking method, considers an exhaustive state and fault space. Krautz et al [45] used formal verification to exhaustively measure the fault coverage of a VHDL design. Symbolic simulation of sequential circuits are performed by creating Binary Decision Diagrams of the circuit's state space. The BDD analysis helps in identifying the fault detection/correction capability of each state in the system and quantitatively classify them, after a fault injection. This fault injection module (FIM) exhaustively covers only the state space and not the input data space. The input data and faults are fed into the FIM as bit vectors. Leveugle [46] introduced the new approach of combining property with mutation of the circuits to conduct fault injection experiments on circuits. Mutants of VHDL circuits that exhibit faulty behavior similar to the ones expected in the field

are prepared through a controlled generation approach. Critical properties are checked for any violations in the mutated circuits thereby helping in identifying the undesirable effects of multiple faults in the circuit. Several commercial tools for property checking, in particular Verifier from Safelogic and FormalCheck from Cadence are used for his experiments. Daniel et al [47] was the first one to demonstrate the effectiveness of symbolic fault injection on an SIHFT application in Java platform. This simulation based fault injection approach involves the injection of symbolic faults during the symbolic execution of the software. Transient bit flips in the data memory variables are simulated by executing pseudo statements in the code during symbolic execution of the code. The critical properties of the software are proven for validity for all inputs and all modeled faults using formal software verification tools like KeY. All the above referenced works have combined fault injection on hardware design with formal verification. Whereas, this thesis focuses on applying the fault injection based on formal verification principles at the functional model level.

There are few works in the literature on model based fault injection. MODIFI [48] is a model implemented GUI based fault injection tool which gives a good level of fault injection controllability and observability on Simulink behavior models. Fault models are derived from XML descriptions and implemented as Matlab code in the saboteurs inserted in the fault location during runtime. The evaluation of the FI experiments are carried out either by using runtime assertions or by comparison with nominal behavior. MODIFI additionally facilitates minimal cut set analysis to find the minimal set of faults that violate a safety requirement. Moradi et al in [49] presents another automated fault injection framework in Simulink model based environment. The model is annotated by the designer with custom FI blocks that can be configured with the type of fault, fault injection time, duration and other parameters. These annotations are transformed into saboteurs and then the FI experiments are run one by one on the FI deployed model using an FI orchestrator script. In addition to hardware faults, the authors of this work also consider software faults that include code insertion and code drop as well as latency which are not considered in [48]. Pill et al in [50] proposed a toolset SIMULTATE that combines fault injection and mutation testing on Simulink behavioral models. The fault library mainly consists of structural mutations to blocks in the model, that include adding new block, replacing blocks and rerouting signal connections. The major advantage of this toolset is its flexibility to easily support custom fault models. In all of these model-based fault injection frameworks, though the saboteur insertion is automated, the placement of saboteurs is decided by the modeler and therefore the FI tests could end up in insufficient fault coverage problems. FI experiments conducted in a classical FI approach, with the need to feed in input vectors for executing the model, suffers from incomplete input, state and fault space coverage.

# **Chapter 4 Overview of the Representative System**

This short chapter gives a brief overview of the representative safety critical system on which the model-based design assurance workflow and the property based fault injection are applied. The target system in this study is a FPGA-based digital I&C architecture for safety critical applications in nuclear power plants.

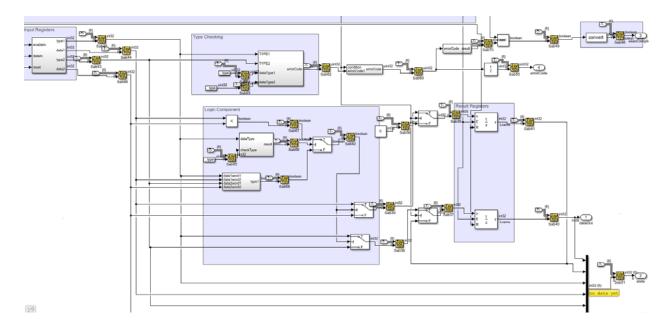

SymPLe architecture [51] was created to solve the risk of software common cause failures when transitioning from analog to digital technology in safety-related instrumentation and control applications in nuclear power plants. Specifically, SymPLe is a notational architecture designed in a MBE environment which aims to ease verification of digital systems using complexity-aware design and design-for-verification principles. SymPLe is a portable FPGA overlay architecture for PLC computation. SymPLe is programmed with a Function Block language similar to IEC-1131 PLC programming languages. The adoption of PLC's function block programming notation in SymPLe was due to the long history of PLCs in safety and non-safety operations in nuclear power. The constrained and complexity-aware SymPLe design supports deterministic execution of elementary functions, known as Function Blocks. This helps in porting the SymPLe architecture into existing PLC applications which are common in nuclear power and other process control applications. Figure 4 shows an overview of the SymPLe architecture.

The design of SymPLe is implemented in three basic control hierarchies: the global sequencer, local sequencers or tasks, and a complete set of Function Blocks (FB) per local sequencer/task. In SymPLe, each task lane execution happens independent of the other tasks. The global sequencer (GS) is the highest controlling component of the architecture. The global sequencer is responsible for coordination of each task and the marshaling of data to/from task registers from/to IO points in the architecture. Triggering task lane execution is the responsibility of the scheduler contained in the GS. During the initialization of the architecture, the GS reads from the global sequence and sets the task schedule or hard deadline for each task, initializes task memory locations, and initializes outputs of the system. Following this, all system inputs are read into the system and task lanes are executed. When a non-recoverable error is encountered in the architecture, the GS transitions to the failed state in which the architecture terminates task executions and all outputs are put in a safe state. SymPLe architecture implements fail-stop and fail-safe behavior in this manner.

Each task contains a local sequencer, a function block controller, a set of function blocks, and a redundant memory. The local sequencer is the controller for the task lane. It reads the task sequence programmed by the user and schedules the execution of the function blocks as per the user-provided deterministic sequence to implement the application in the task. The local sequencers' function is to marshal data to/from task registers and from/to function block registers and to sequentially trigger function blocks in its own task lane. The local sequencer is implemented using state flow diagrams with several main and sub states. The main states within Local sequencer state machine are INIT, FB\_SELECT, FETCH, FB\_EXECUTE, WRITE, FB\_DONE, TASK\_DONE and ERROR. If an error detected during function block execution is identified as a recoverable error, the local sequencer retries by restarting the FB execution. If the error is identified as non-recoverable, Local Sequencer informs Global Sequencer and the GS triggers an abort of the current task execution and restarts the entire task sequence. The FB Controller supervises and controls the execution process of the selected function block. It is implemented as a state machine with states mirroring those of the local sequencer. Functions blocks receive data into shift registers, process the data as per intended functionality, and computes and writes results in their output registers.

Figure 4: The SymPLe Architecture [42]

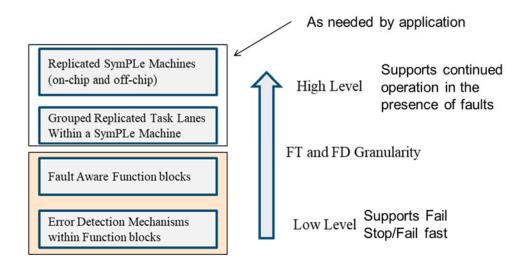

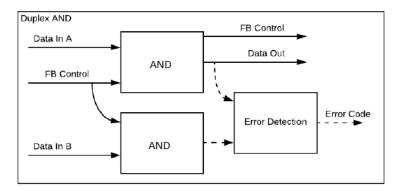

Function Blocks are the elementary "program or computation" units that SymPLe architecture employs for its program organization or application building. The function block model is derived from two IEC standards – IEC 61131-3, and IEC 61499. The 32 different function blocks implemented in SymPLe architecture to aid in application building are given in Table 1. As shown in Figure 5, the fault detection and tolerance mechanisms in SymPLe architecture starts at the lowest level of architecture which is the function blocks thereby allowing the system to enter a fail-stop state before the error propagates beyond boundaries of the system.

Table 1: Implemented Function Blocks in SymPLe [51]

| Operation<br>Type  | Functionality                                      | Valid Data Type(s) |

|--------------------|----------------------------------------------------|--------------------|

| Binary             | NOR,AND,NOT,OR,XOR,NAND                            | BOOL,SAFEBOOL      |

| Bitwise            | BNOR,BAND,BNOT,BOR,BXOR,BNAND,BSL,BSR              | INT                |

| Comparison         | MAX,MIN,MUX,GT,GE,EQ,LT,LE,NE                      | INT,QMN            |

| Arithmetic         | ADD,SUB,MUL,DIV                                    | INT,QMN            |

| System             | MOV                                                | Any                |

| Type<br>Conversion | QMNtoINT, INTtoQMN, BOOLtoSAFEBOOL, SAFEBOOLtoBOOL | Various            |

Figure 5: Fault Tolerance Approach for SymPLe [51]

# **Chapter 5 Model Based Engineering and Design Assurance**

This chapter gives an overview on Model based Engineering and Design and the general model based Design assurance workflow for safety critical systems, starting from textual requirements to the hardware implementation, from a Mathworks perspective. The different choices of MBD tools available and the challenges faced in the development of the end to end design assurance workflow for the representative architecture are also presented in this chapter. This chapter then presents an overview of the Model based Design Assurance workflow developed for SymPLe architecture, and then a more detailed discourse on the different stages of Model testing process that involves, unit, integration and system testing. The chapter also gives key examples of test failures caught in the process of model testing and highlight the capabilities of model simulation and testing in finding a number of critical design flaws in the model.

#### 5.1 Model-based Engineering and Design

Model Based Design and Engineering is not a new practice, but has evolved over years to be a discipline in itself – merging various scientific computing and engineering disciplines together to provide a comprehensive approach to engineering and integrating complex systems. We note the phrase "Model Based Design" has been used in many different contexts to the point where it's meaning and purpose is somewhat unclear. For safety critical systems design, we use a more refined definition taken from the systems engineering and the formal methods community.

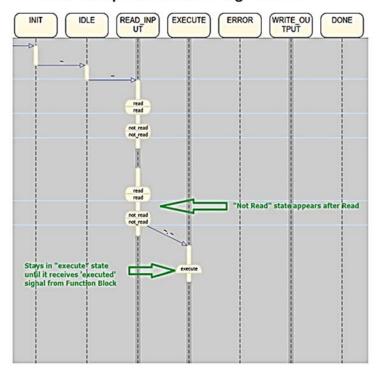

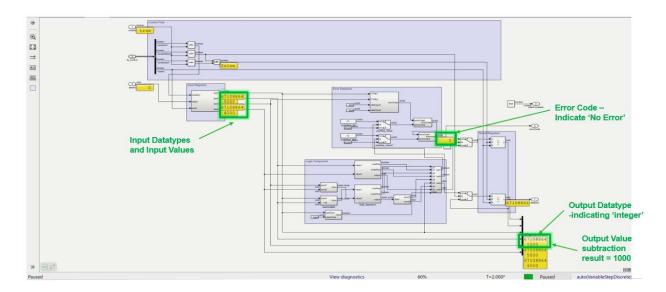

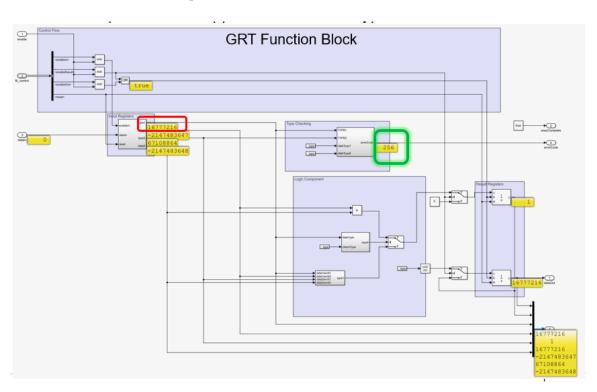

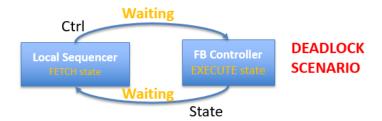

"Model Based Design Engineering (MBDE) is the formalized application of modeling to support system requirements, design, analysis, verification and validation activities beginning in the conceptual design phase and continuing throughout development and later life cycle" [52]