### Virginia Commonwealth University **VCU Scholars Compass**

Theses and Dissertations

Graduate School

2020

# Multilevel Runtime Verification for Safety and Security Critical Cyber Physical Systems from a Model Based Engineering Perspective

Smitha Muralidhar Gautham

Follow this and additional works at: https://scholarscompass.vcu.edu/etd

Part of the Electrical and Computer Engineering Commons

© The Author

#### Downloaded from

https://scholarscompass.vcu.edu/etd/6481

This Dissertation is brought to you for free and open access by the Graduate School at VCU Scholars Compass. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of VCU Scholars Compass. For more information, please contact libcompass@vcu.edu.

# Multilevel Runtime Verification for Safety and Security Critical Cyber Physical Systems from a Model Based Engineering Perspective

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering at Virginia Commonwealth University.

by Smitha Muralidhar Gautham

Master of Science

Department of Electrical and Computer Engineering

Virginia Commonwealth University, 2010

Bachelor of Engineering

Department of Electronics and Communication Engineering

PES Institute of Technology, 2007

Director: Dr. Carl R. Elks

Associate Professor, Department of Electrical & Computer Engineering

Virginia Commonwealth University

Richmond, Virginia

## **Dedication**

In loving memory of my grandparents

Nagarathnamma and Narayana Murthy

Rathnamma and Bhaskar Rao

## Acknowledgement

First and foremost, I would like to express my sincere gratitude to my advisor Dr. Carl Elks for his constant support and encouragement over the years. It's has been a privilege to be his student and I have learnt a lot from him. He has been extremely encouraging and an understanding advisor. Without his guidance and help, this dissertation would not have been possible. I would like to thank my PhD committee Dr. Barry Johnson, Dr. Robert Klenke, Dr. Ashraf Tantawy and Dr. Preetam Gosh for their support and valuable feedback on my research.

I would like to thank the Department of Energy, Division of Advanced Sensors and Instrumentation (DOE ASI) and Electric Power Research Institute (EPRI) for funding me on the SymPLe project. I would like to thank Matt Gibson of EPRI for his support and advice on the SymPLe project. I would like to express my sincere thanks to Ken Thomas of Idaho National Laboratories for his support and the opportunity to work on the Bounded Exhaustive Testing project.

I would like to thank the Institute for Software Engineering and Programming Language, University of Lubeck for their help with the TeSSLa tool. I am also honored to work with Dr. Alexander Weiss from Accemic Technologies, and Dr. Richard D Kuhn and Dr. Raghu N Kacker of National Institute of Standards and Technology (NIST). I am thankful to Dr. Alwyn Goodloe from NASA Langley Research Center for his encouragement and insights on runtime verification.

It would like to thank all by colleagues in the VCU Dependable Cyber Physical Systems Laboratory. They are the best team I could have ever had and were always willing to help out. I would like to thank the SymPLe team Athira Varma Jayakumar, Richard Hite, Christopher Deloglos and Dr. Ashraf Tantawy, I have enjoyed every discussion that we had and it is very fulfilling to see the SymPLe project grow. Athira has been a great friend and I have learnt so much from her. Her work on fault injection has been extremely useful for my research and I will cherish all the stimulating discussions that we have had. I would like to thank Dr. Rajagopala for being a great mentor, his guidance has been valuable for my research. I would like to thank Tamara Pena, Aidan Collins, Brandon Simon and Erwin Karincic for their help.

I am very lucky to have my friends Priya, Meera, Shravanthy and Mrugaya who have always been there to cheer me up and make me smile.

My family has stood by me through thick and thin. Their support and encouragement has helped me more than I can express. I would like to thank my parents Latha and Muralidhar for always being there for me. They have taken pride in every little thing I have achieved and their love and blessings has taken me far in life. They have been my role model and my guiding force. I would like to thank my in-laws Anupama and Jayasimha for all their love and blessings. They have been a source of encouragement and support.

I would like to thank my siblings Sapna and Sharath for being my best friends. They are always there rooting for me and wishing me the best. My sister-in-law Nirupama is the smartest and sweetest person I know. She is my 'go-to person' for any advice and has been a constant support. I would also like to thank Hemant, Sudhanva and Ketaki for their best wishes. My little nephews and nieces Siddanth, Lasya, Shourya have inspired me in their own cute ways, always making me happy.

Lastly, I would like to thank my dear husband Atul and my two beautiful kids Advaith and Ananya for their unconditional love and encouragement. I am extremely grateful to my husband Atul for giving me the time to do my research by taking care of the kids and pepping me up with coffee so I could stay up late to finish my work. I am very lucky to have such a loving husband. A big hug to my wonderful kids Advaith and Ananya, for being so understanding and always bringing me a smile!

# **Table of Contents**

| List of Figures                                                                            | 10   |

|--------------------------------------------------------------------------------------------|------|

| List of Tables                                                                             | 13   |

| Publications                                                                               | 14   |

| List of Abbreviations                                                                      | 16   |

| Chapter 1                                                                                  | 21   |

| Introduction                                                                               | 21   |

| 1.1 Background                                                                             | 21   |

| 1.2 Motivation: Example Incidents and Problems                                             | 22   |

| 1.3 Runtime Verification for CPS                                                           | 24   |

| 1.4 Integration of Design and Operational Phases to achieve Dependability: DepDevOps       | 26   |

| 1.4.1 A Conceptual View of Integrating Design Development and Runtime Verification for CPS | \$27 |

| 1.5 Critical Issues                                                                        | 28   |

| 1.5.1 Observation of target system                                                         | 28   |

| 1.5.2 Safety and Security – How to do both, if possible?                                   | 30   |

| 1.5.3 The Specification of Safe and Secure – Where does it come from?                      | 31   |

| 1.6 Need for Multilevel Monitoring of the Target System                                    | 31   |

| 1.7 Problem Statement                                                                      | 33   |

| 1.8 Goal and Objectives                                                                    | 34   |

| 1.9 Contributions and Scope of this Research                                               | 34   |

| 1.10 Roadmap of Research                                                                   | 35   |

| Chapter 2                                                                                  | 37   |

| Related Work                                                                               | 37   |

| 2.1 Verification and Validation(V&V) of Design                                             | 37   |

| 2.2 Synergy between design and runtime verification                                        | 38   |

| 2.2.1 Design Verification guides runtime monitor design                                    | 38   |

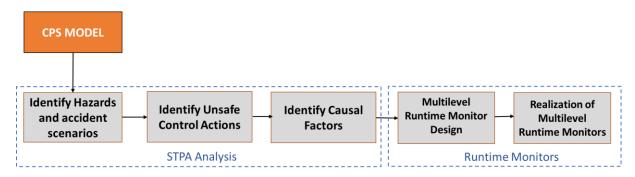

| 2.2.2. STPA analysis guides runtime monitor design                                             | 39 |

|------------------------------------------------------------------------------------------------|----|

| 2.3 Runtime Monitors                                                                           | 39 |

| Chapter 3                                                                                      | 42 |

| A Framework for the Design and Development of Multilevel Monitoring in Cyber Physical Systems. | 42 |

| 3.1 Introduction                                                                               | 42 |

| 3.2 Critical Cyber Physical Systems                                                            | 43 |

| 3.3 Concepts of Dependability and Security                                                     | 44 |

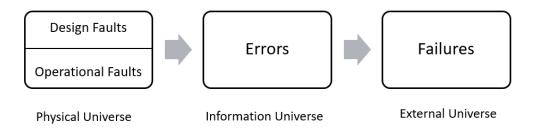

| 3.3.1 The Three Universe Model: Faults, Errors, and Failures                                   | 45 |

| 3.3.2 Classification of Attacks in Cyber Physical Systems                                      | 48 |

| 3.4 Formal Development of Multilevel Monitoring Framework                                      | 51 |

| 3.4.1 A CPS Reference Architecture                                                             | 51 |

| 3.5 Justification for Multilevel Monitors for detection of attacks/failures                    | 53 |

| 3.6 Formal Model of Multilevel Monitoring                                                      | 57 |

| 3.7 A High-Level View of Monitoring Approaches                                                 | 67 |

| 3.7.1 In-situ vs. External Monitors                                                            | 68 |

| 3.7.2 Organization of Monitors                                                                 | 69 |

| 3.8 Practical considerations: realization of monitors                                          | 72 |

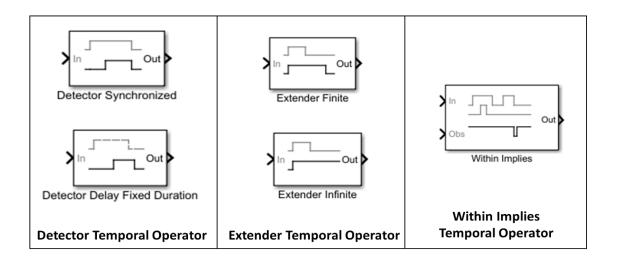

| 3.8.1 TeSSLa Runtime Verification Language                                                     | 72 |

| 3.9 Bridging the gap between design time V&V with Runtime Monitoring                           | 75 |

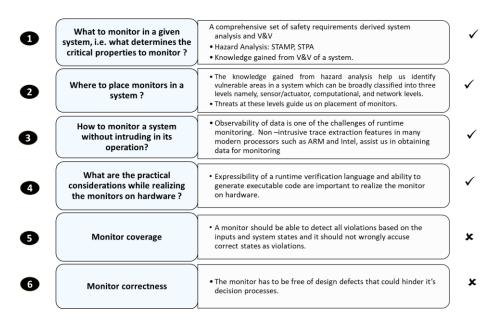

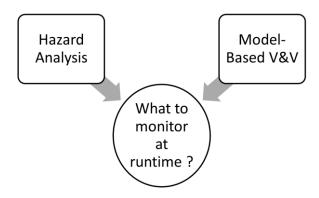

| 3.9.1 Hazard Analysis                                                                          | 76 |

| 3.9.2 Model-Based V&V                                                                          | 78 |

| 3.10 Other considerations in runtime monitor design                                            | 79 |

| 3.11 Towards a Systematic Framework for Multi-level Monitoring                                 | 80 |

| Chapter 4                                                                                      | 82 |

| Synergy between Design Assurance using Model based Engineering and Runtime Verification        | 82 |

| 4.1 Introduction and purpose                                                                   | 82 |

| 4.2 Model_Based Engineering                                                                    | 83 |

| 4.3 Connection between Design time Assurance and Runtime Verification                          | 85  |

|------------------------------------------------------------------------------------------------|-----|

| 4.4 Representative System to Explore Synergy                                                   | 89  |

| 4.4.1 Emergency Diesel Generator Start Up Sequencer (EDGSS)                                    | 89  |

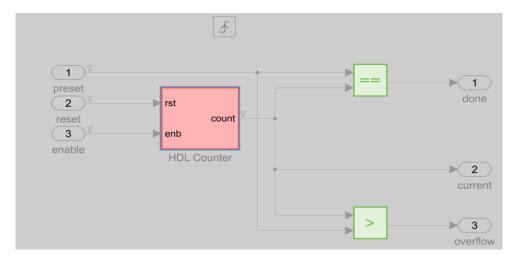

| 4.4.2 SymPLe: An FPGA overlay architecture                                                     | 90  |

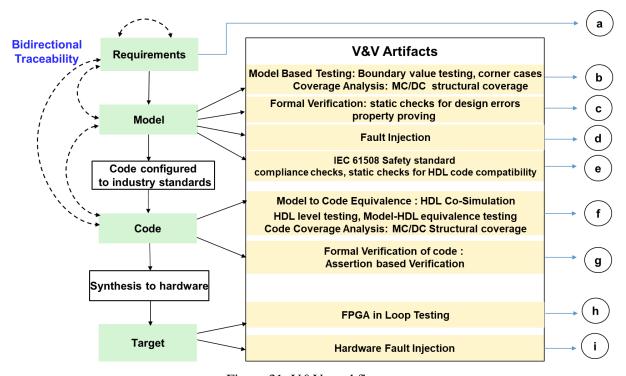

| 4.5 Design Assurance using Model Based Engineering (MBE)                                       | 92  |

| 4.5.1 Design Assurance Workflow                                                                | 93  |

| 4.6 Implementation of Monitors Based on Synergy                                                | 104 |

| 4.7 Findings on Synergy from V&V of Model Based Designs                                        | 108 |

| Chapter 5                                                                                      | 111 |

| Design and Evaluation of Multilevel Runtime Monitoring using Model-based Engineering Methods . | 111 |

| 5.1 Introduction and Purpose                                                                   | 111 |

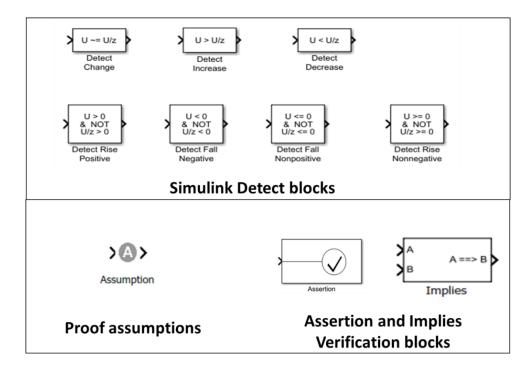

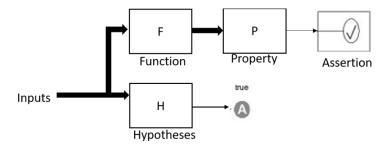

| 5.2 MathWorks Simulink Verification Blocks                                                     | 111 |

| 5.3 Specifying monitoring properties using Event Calculus                                      | 113 |

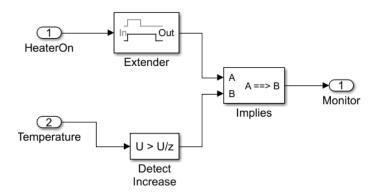

| 5.4 Example CPS: Anti-lock Braking System (ABS)                                                | 115 |

| 5.4.1 Rationale for monitor placement in the ABS                                               | 115 |

| 5.4.2 Monitoring properties for ABS controller expressed using Event Calculus                  | 116 |

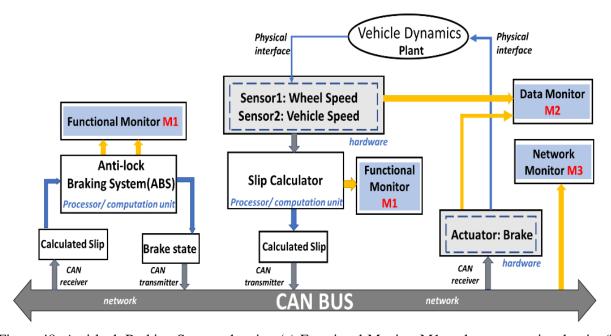

| 5.5 Evaluation of Multilevel Monitors                                                          | 118 |

| 5.6 Discussion: Monitor Organization Patterns                                                  | 126 |

| 5.7 Summary                                                                                    | 130 |

| Chapter 6                                                                                      | 131 |

| ARM Processor Debug and Trace Capability to Assist Multilevel Runtime Monitoring               | 131 |

| 6.1 Introduction and Purpose                                                                   | 131 |

| 6.2 ARM Processor Family                                                                       | 132 |

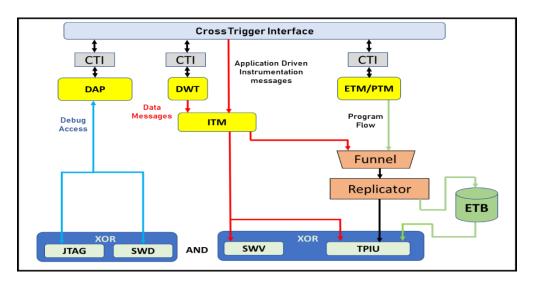

| 6.3 ARM Coresight Architecture Components                                                      | 134 |

| 6.3.1 ARM Trace Infrastructure                                                                 | 134 |

| 6.3.2 ARM Debug Infrastructure                                                                 | 143 |

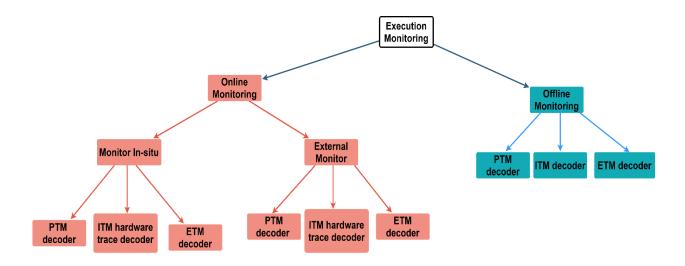

| 6.4 Use of ARM Embedded Trace for runtime monitoring                                           | 143 |

| 6.4.1 Online monitoring                                                                      | 144 |

|----------------------------------------------------------------------------------------------|-----|

| 6.4.2 Offline Monitoring                                                                     | 145 |

| 6.4.3 Trace Decoders                                                                         | 146 |

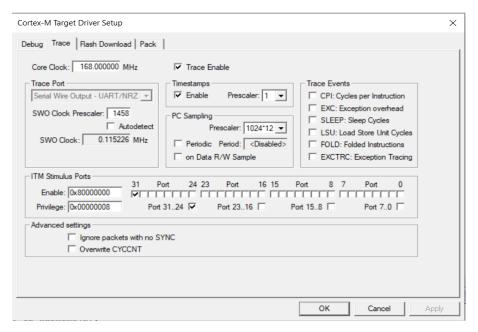

| 6.5 Keil and openOCD ARM development tools                                                   | 151 |

| 6.5.1 Keil Micro Vison                                                                       | 151 |

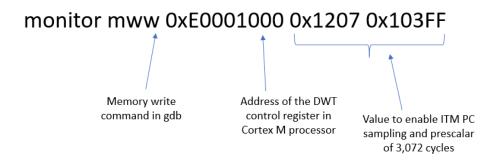

| 6.5.2 OpenOCD                                                                                | 152 |

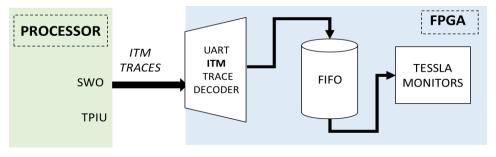

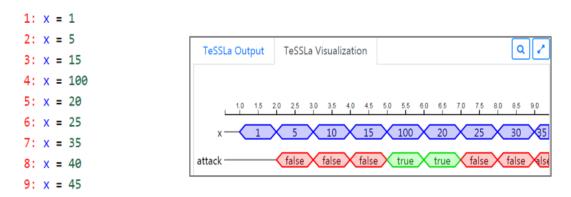

| 6.6 Example of a Functional monitor using ITM trace                                          | 153 |

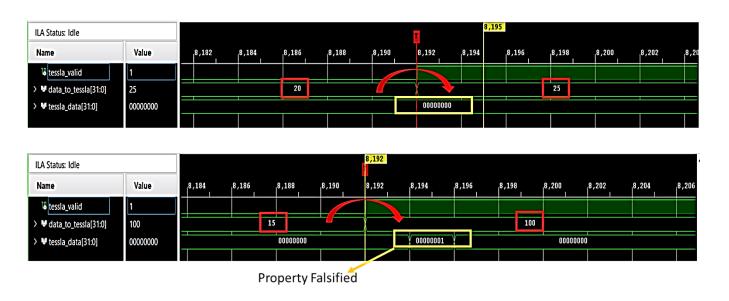

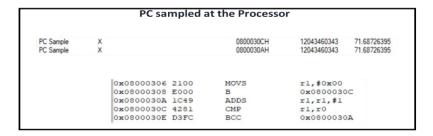

| 6.7 Example of ITM hardware trace decoding which can be used for Execution monitoring        | 156 |

| 6.8 Discussions and Summary                                                                  | 158 |

| Chapter 7                                                                                    | 160 |

| Realization of Multilevel Monitors on Hardware and use of ARM Coresight trace for Functional |     |

| Monitoring                                                                                   | 160 |

| 7.1 Introduction                                                                             | 160 |

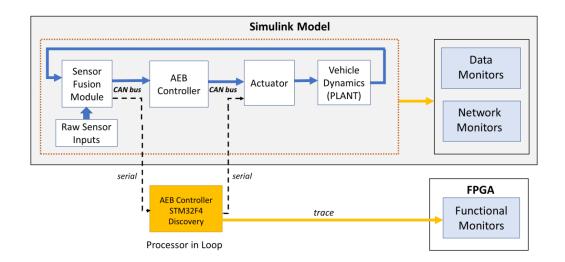

| 7.2 CPS for Multilevel Monitoring: Autonomous Emergency Braking (AEB) controller             | 161 |

| 7.2.1 Simulation Scenario                                                                    | 161 |

| 7.2.2 Examples of threats in an AEB system                                                   | 162 |

| 7.3 Formulating Properties to Monitor at Runtime                                             | 163 |

| 7.4 Faults/attacks and their detection by the monitoring conditions in Simulink              | 166 |

| 7.5 Hardware implementation of Runtime Monitors                                              | 168 |

| 7.5.1 Workflow for generation of monitors                                                    | 168 |

| 7.5.2 Implementation of Monitors                                                             | 169 |

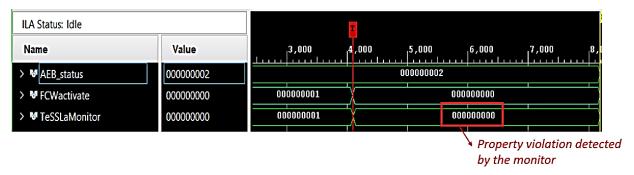

| 7.5.3 Observations                                                                           | 172 |

| 7.6 Functional Monitoring using ARM Embedded Trace                                           | 176 |

| 7.7 Preliminary assessment of scalability of TeSSLa monitors and FIL system components       | 179 |

| 7.8 Summary                                                                                  | 180 |

| Chapter 8                                                                                    | 182 |

| Summary Contributions and Future Work                                                        | 182 |

| 8.1 Key contributions of this dissertations                           | 183 |

|-----------------------------------------------------------------------|-----|

| 8.2 Future work                                                       | 184 |

| Appendix A                                                            | 185 |

| A 1. Model Based Testing and Coverage Analysis of SymPLe architecture | 185 |

| A 2. Simulink Design Verifier                                         | 186 |

| A 3. Safety Standard Compliance checks                                | 187 |

| A 4. Model to Code Equivalence and Code Coverage Analysis             | 189 |

| A 5. Formal Verification of Code                                      | 193 |

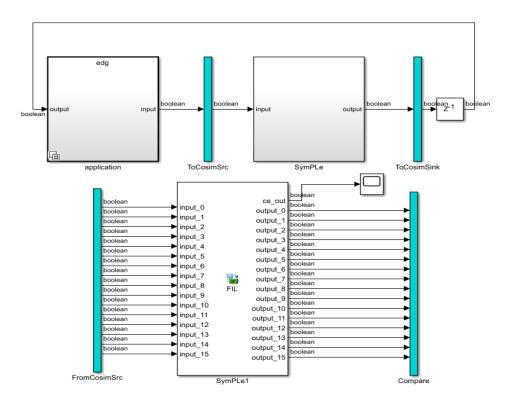

| A 6. FPGA in Loop Implementation of SymPLe                            | 196 |

| A 7. Hardware Fault Injection                                         | 197 |

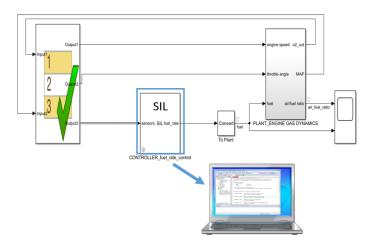

| A 8. Software in Loop (SIL)                                           | 198 |

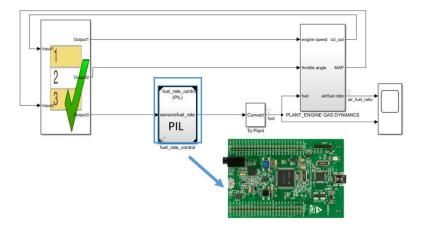

| A 9. Processor in Loop (PIL)                                          | 199 |

| References                                                            | 200 |

# **List of Figures**

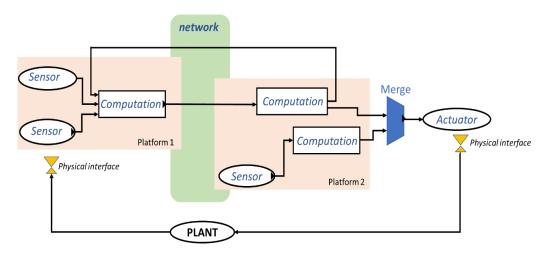

| Figure 1: Cyber Physical System                                                                                 | 22     |

|-----------------------------------------------------------------------------------------------------------------|--------|

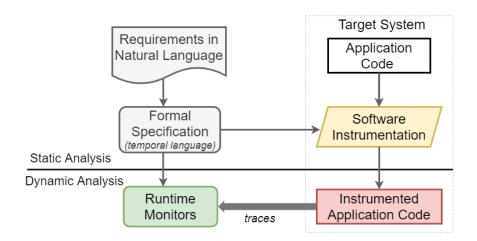

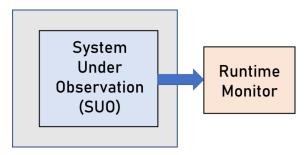

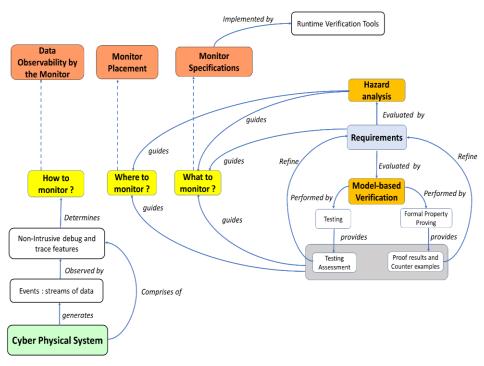

| Figure 2: Runtime verification framework.                                                                       | 25     |

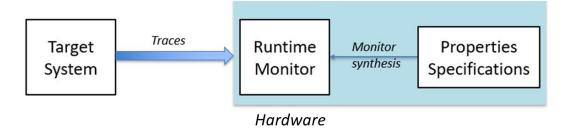

| Figure 3: Overview of runtime verification                                                                      | 26     |

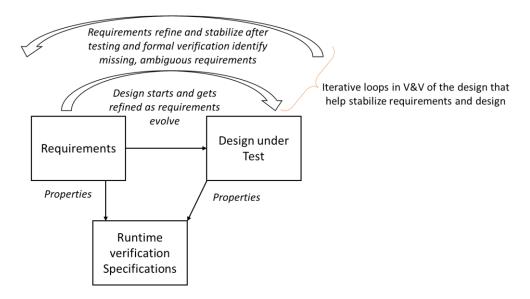

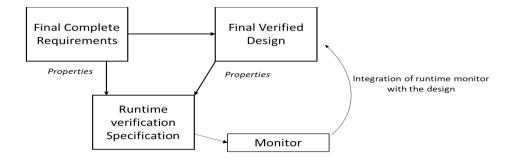

| Figure 4: Phase I – Design: Synergy between Design and Runtime Verification Specifications                      | 28     |

| Figure 5: Phase II – Runtime: Synergy between Design and Runtime Verification Specifications                    | 28     |

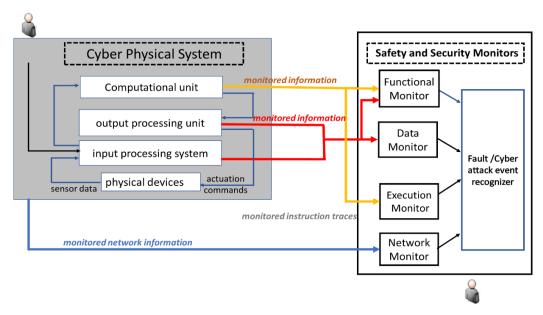

| Figure 6: Multilevel monitoring of a CPS.                                                                       | 33     |

| Figure 7: Workflow toward the realization of Multi-level runtime monitoring.                                    | 42     |

| Figure 8: Three Universe Model                                                                                  | 46     |

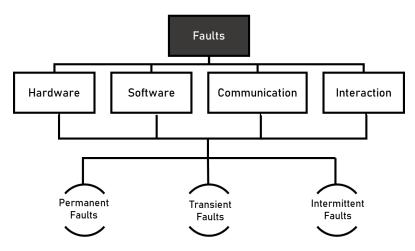

| Figure 9: Classification of faults based in a CPS                                                               | 48     |

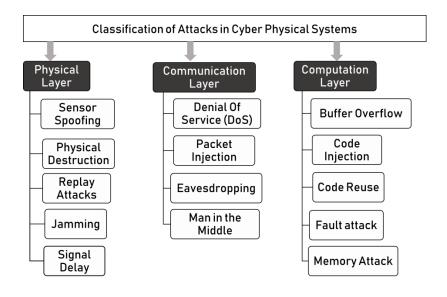

| Figure 10: Taxonomy of Attacks in CPS                                                                           | 50     |

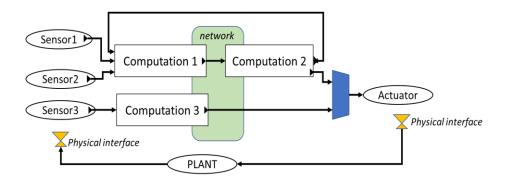

| Figure 11: Structure of a Cyber Physical System                                                                 | 51     |

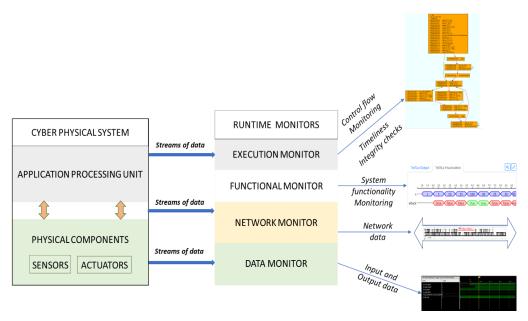

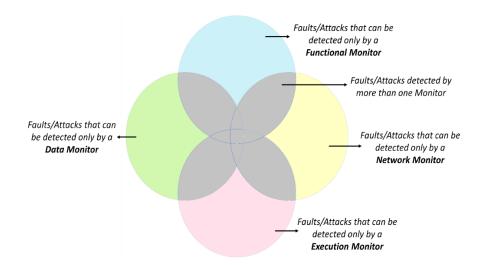

| Figure 12: Multilevel monitoring                                                                                | 55     |

| Figure 13: Need for Attacks/Faults detected by monitors at multiple levels                                      | 55     |

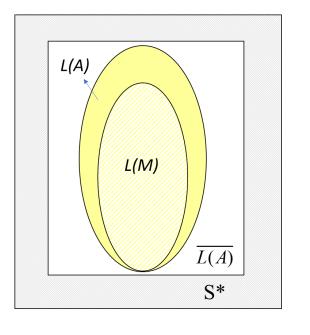

| Figure 14: Language based formal model for runtime monitors [69]                                                | 62     |

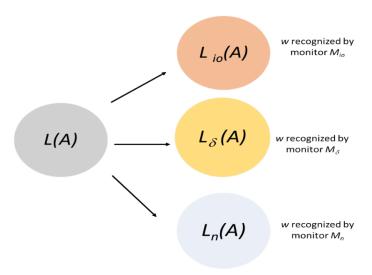

| Figure 15: Words $w$ in the language of the computer-based system $L(A)$ classified into $L_{io}(A)$ , $L_n(A)$ | ) and  |

| $L_{\delta}(A)$ and are recognized by monitors $M_{io}$ , $M_n$ and $M_{\delta}$ respectively.                  | 64     |

| Figure 16: In-situ Monitor                                                                                      | 68     |

| Figure 17: External Runtime Monitor                                                                             | 69     |

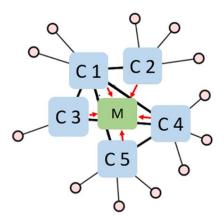

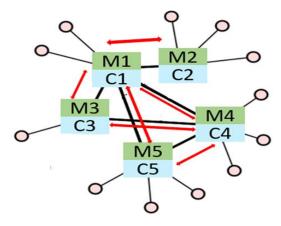

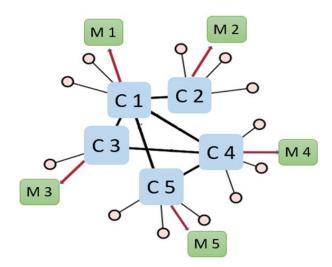

| Figure 18: Monolithic Monitoring                                                                                | 70     |

| Figure 19: Distributed Monitoring                                                                               | 71     |

| Figure 20: Heterogeneous Monitoring                                                                             | 71     |

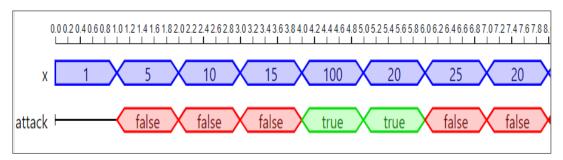

| Figure 21: Stream of data indicating position and monitor indicating attack                                     | 73     |

| Figure 22: Snippet of the TeSSLa specification.                                                                 | 73     |

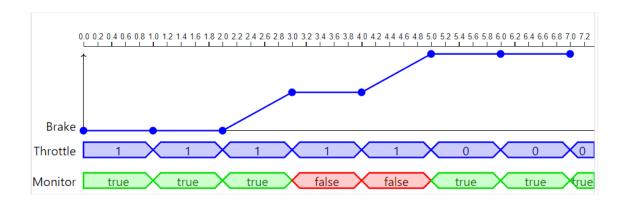

| Figure 23: TeSSLa Monitor output that verifies the property to ensure correct throttle action                   | 74     |

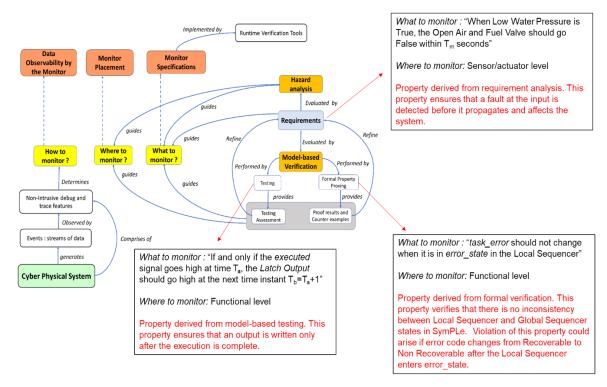

| Figure 24: STPA hazard analysis and Model based V&V inform us on "what to monitor" at runtin                    | ne and |

| placement of monitors                                                                                           | 76     |

| Figure 25: Conceptual view of STPA driven Runtime Monitor                                                       | 78     |

| Figure 26: Runtime monitor framework                                                                            | 81     |

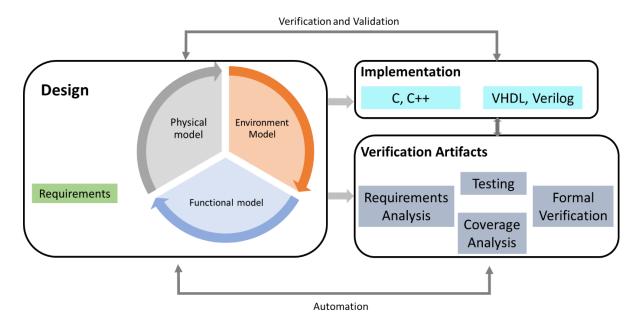

| Figure 27: Basic elements of a Model Based Engineering design. (inspired by [94])                               | 85     |

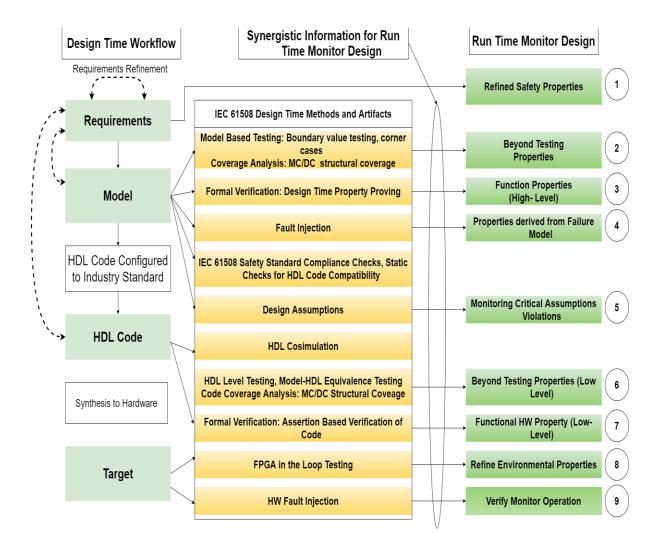

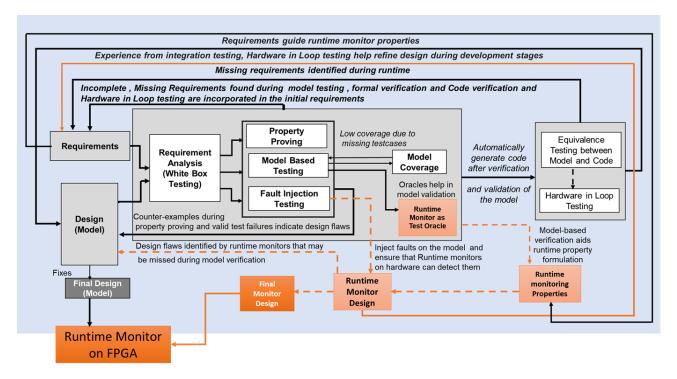

| Figure 28: V&V workflow to explore synergy                                                                      | 87     |

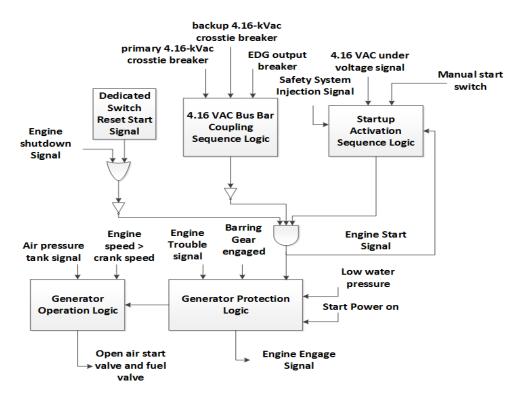

| Figure 29: High Level model of the Emergency Diesel Generator Startup Sequencer                                 | 90     |

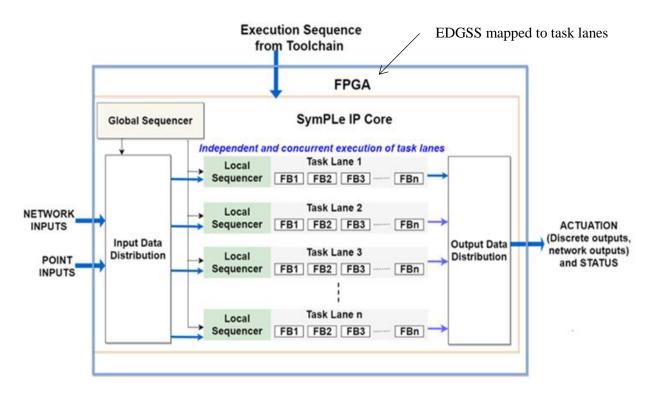

| Figure 30: FDGSS implemented on SymPLe architecture                                                             | 91     |

| Figure 31: V&V workflow                                                                      | 93  |

|----------------------------------------------------------------------------------------------|-----|

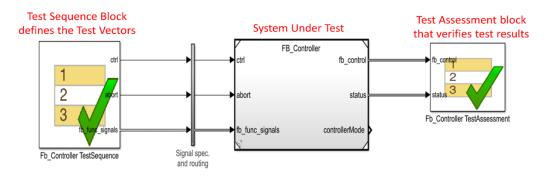

| Figure 32: Simulink Test Sequence block and Test Assessment block                            | 96  |

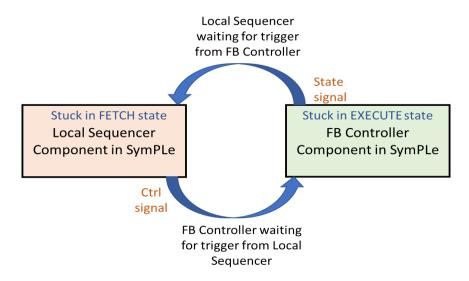

| Figure 33: Model Based Testing detects Deadlock scenario                                     | 97  |

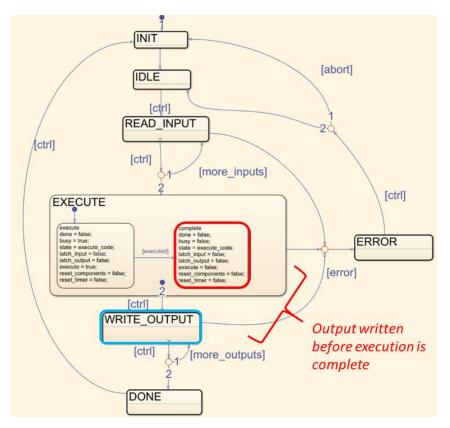

| Figure 34: Transition to write_output state before execution is complete                     | 98  |

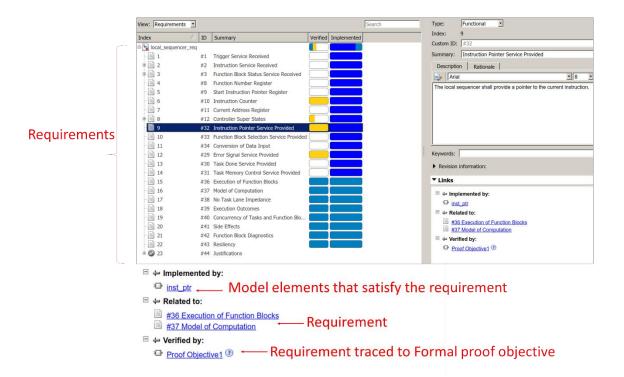

| Figure 35: Bi-directional traceability between requirements, model and formal proofs         | 99  |

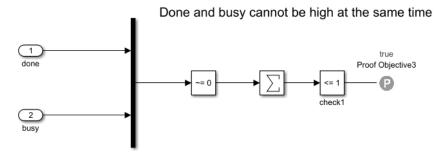

| Figure 36: Simulink Design Verifier property                                                 | 100 |

| Figure 37: Design Verifier property to verify valid transition.                              | 101 |

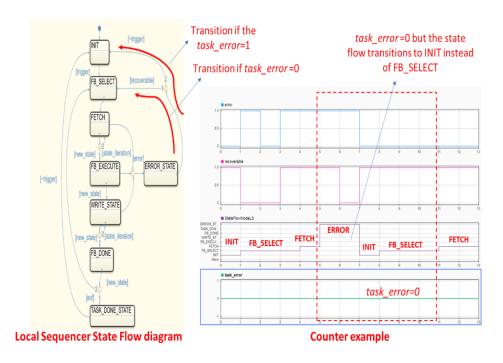

| Figure 38: Counter-example showing invalid transition due to design issue in error handling  | 101 |

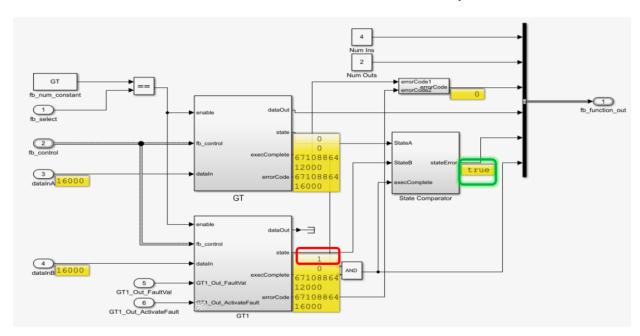

| Figure 39: Fault Injection on Greater Than Functional Block in SymPLe architecture           | 102 |

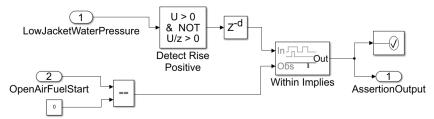

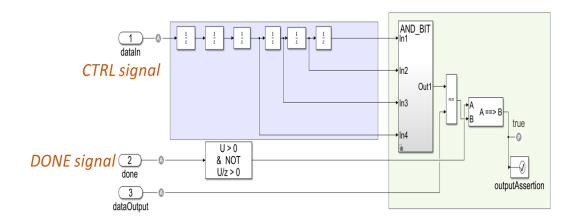

| Figure 40: Runtime monitor property modeled using Simulink verification blocks               | 103 |

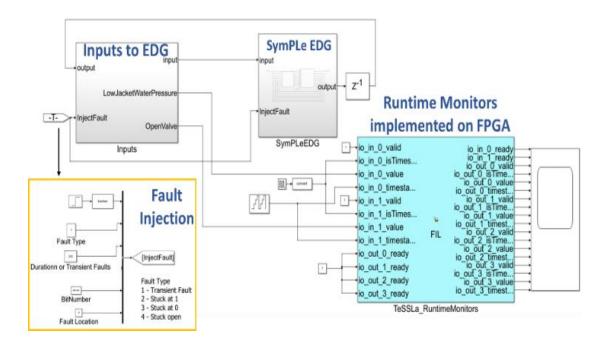

| Figure 41: EDGSS model verified using TeSSLa Runtime monitors                                | 105 |

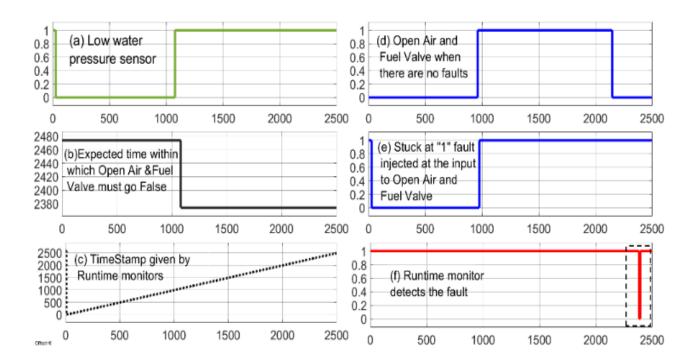

| Figure 42 : Stuck-at "1" fault injected on EDGSS model and detected by the monitor           | 106 |

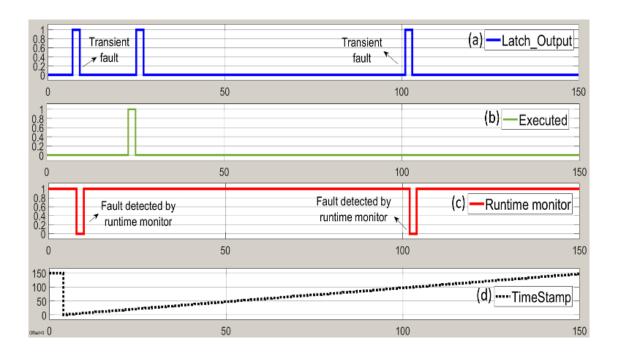

| Figure 43: Transient Faults injected on SymPLe and detected by the monitor                   | 107 |

| Figure 44: Iterative workflow shows synergy between Design verification and runtime monitors | 108 |

| Figure 45: Model-based verification guides 'what to monitor' and 'where to monitor'          | 110 |

| Figure 46: Simulink temporal blocks, proof assumptions, assertion and Implies blocks         | 113 |

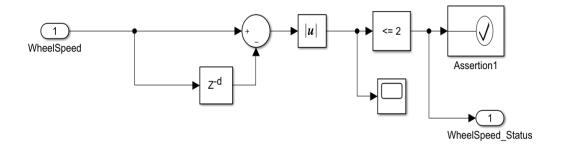

| Figure 47: Implementation of a property using Simulink blocks.                               | 115 |

| Figure 48: Anti-lock Braking System.                                                         | 116 |

| Figure 49: Fault Saboteurs injected in the ABS.                                              | 119 |

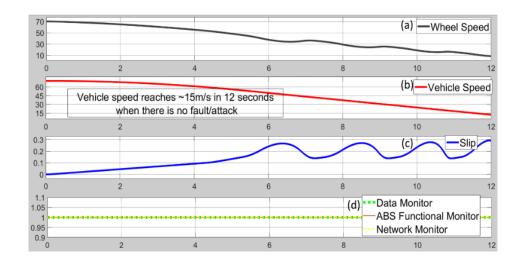

| Figure 50: No attack/fault on the CPS.                                                       | 120 |

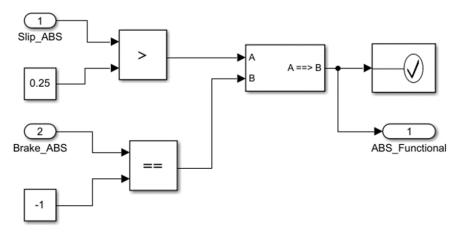

| Figure 51: Property 1 modeled in Simulink, verified by the Functional Monitor M1             | 121 |

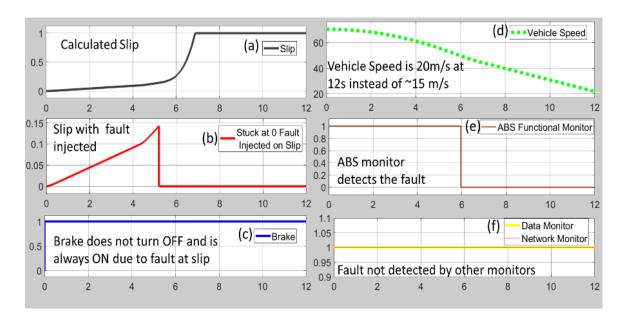

| Figure 52: Stuck at 0 fault on the ABS controller                                            | 121 |

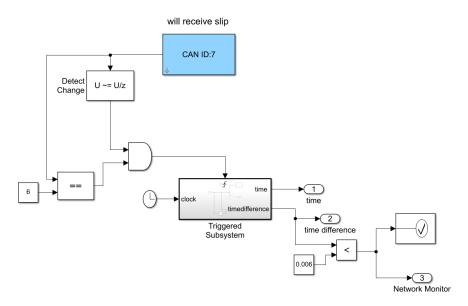

| Figure 53: Property 3 modeled in Simulink, verified by the Network Monitor M3                | 122 |

| Figure 54: Bus traffic delay detected by Network monitor.                                    | 123 |

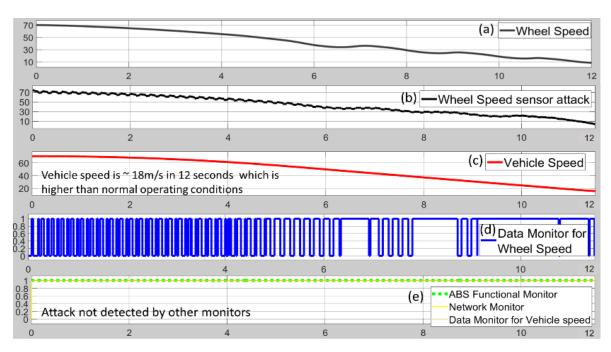

| Figure 55: Property 2 modeled in Simulink, verified by the Data Monitor M2                   | 123 |

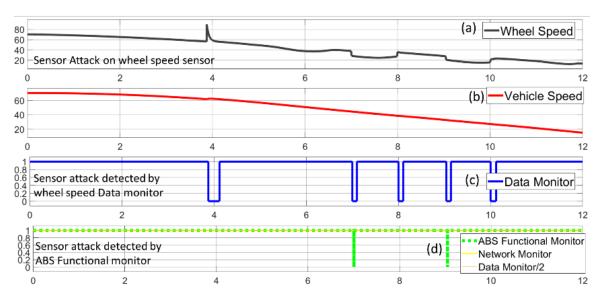

| Figure 56: Attack on wheel speed sensor detected by monitor.                                 | 124 |

| Figure 57: Attack detected by multiple monitors.                                             | 125 |

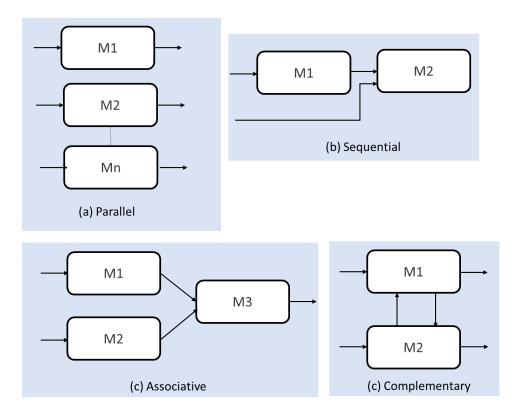

| Figure 58: Parallel, Sequential, Associative and Complementary monitor organization.         | 126 |

| Figure 59: ARM Coresight Architecture                                                        | 134 |

| Figure 60: ETM trace viewed on a Keil Micro Vision IDE                                       | 139 |

| Figure 61: Design choices for execution monitoring that use ARM Coresight Debug and Trace    | 144 |

| Figure 62: An example OpenCSD decoded trace for an ETMv4 trace                               | 149 |

| Figure 63: Enabling debug and trace features in Cortex M processor using Keil IDE            | 152 |

| Figure 64: Configuring DWT/ITM with OpenOCD.                                                 | 152 |

| Figure 65: Sending ITM traces from ARM Processor via the SWO to the monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 153      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 66: TeSSLa specification to check for change in x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 154      |

| Figure 67: (a) Input trace for variable x (b) TeSSLa monitor output to detect change in x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 155      |

| Figure 68: TeSSLa monitor output on the FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 155      |

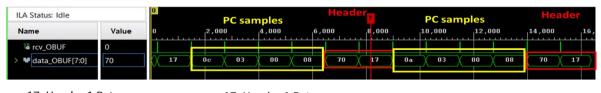

| Figure 69: PC sample decoded on the FPGA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 156      |

| Figure 70: Offline decoded ITM PC sampling data in Cortex M devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 157      |

| Figure 71: Profiling information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 158      |

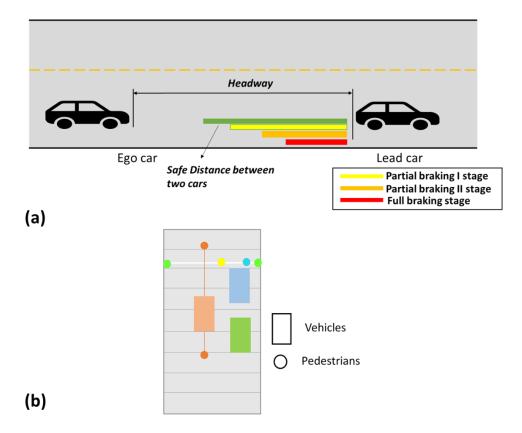

| Figure 72: AEB system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 162      |

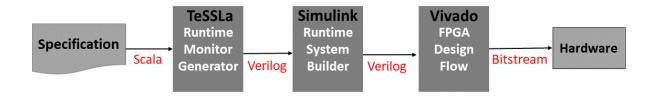

| Figure 73: Workflow for generation of TeSSLa monitors and integrating with Simulink model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 169      |

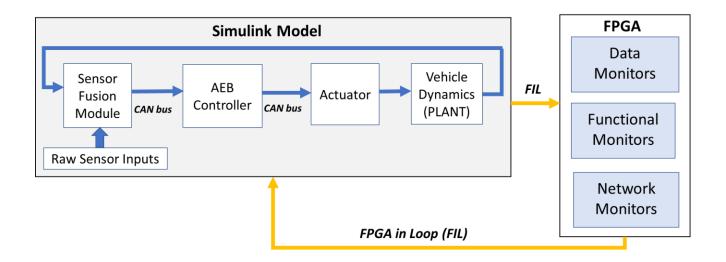

| Figure 74: Schematic showing the AEB controller, plant, and sensors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 170      |

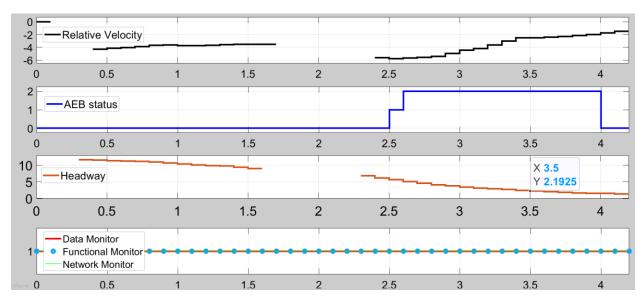

| Figure 75: No fault/attack in the AEB system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 173      |

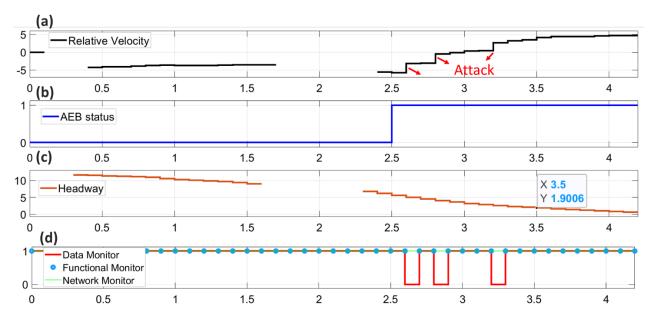

| Figure 76: Data monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 174      |

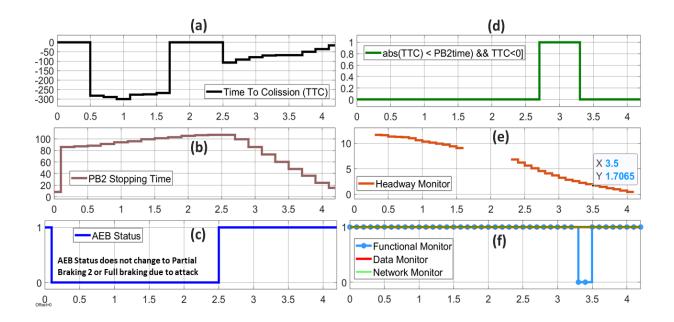

| Figure 77: Functional monitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 175      |

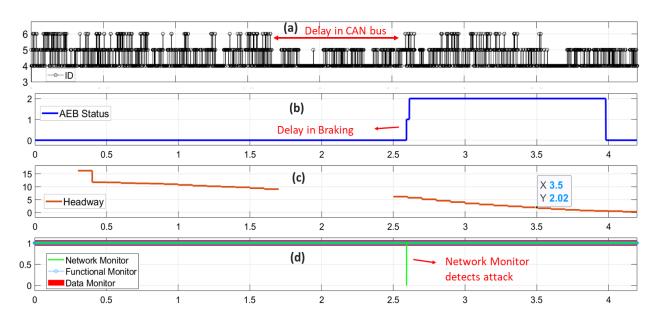

| Figure 78: Network monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 176      |

| Figure 79: AEB controller implemented on an ARM Cortex M4 processor and verified by TeSSLa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ì        |

| monitors on the FPGA. Plant and sensors are simulated on the Simulink model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 177      |

| Figure 80: TeSSLa property that verifies the relationship between AEB_status and FCW active significant states are stated as a second state of the relationship between AEB_status and FCW active significant states are stated as a second state of the relationship between AEB_status and FCW active significant states are stated as a second state of the relationship between AEB_status and FCW active significant states are stated as a second state of the relationship between AEB_status and FCW active significant states are stated as a second state of the relationship between AEB_status and FCW active significant states are stated as a second state of the relationship between AEB_status and FCW active significant states are stated as a second state of the relation states are stated as a second state of the relation states are stated as a second state of the relation states are stated as a second state of the relation states are stated as a second state of the relation states are stated as a second state of the relation states are stated as a second state of the relation state of the relation states are stated as a second state of the relation stated as a second state of the relation stated as a second state of the relation stated as a second stated stated as a second stated as a second stated stated stated as a second stated stated stated stated as a second stated | gnal 178 |

| Figure 81: TeSSLa input and output streams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 178      |

| Figure 82: TeSSLa monitor verifies an AEB property                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 179      |

| Figure 83: Low coverage indicated in Simulink blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 185      |

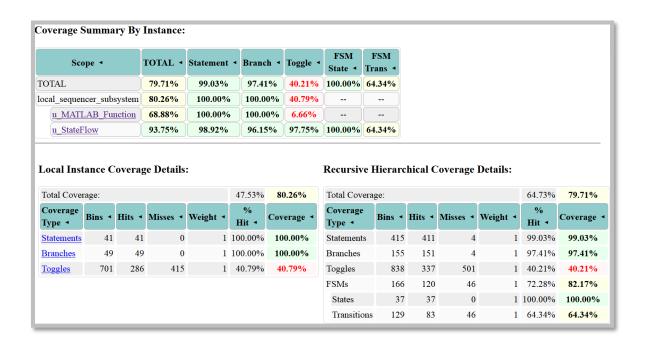

| Figure 84: Coverage Analysis of SymPLe component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 186      |

| Figure 85: General Proof Outline for Simulink Design Verifier .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 187      |

| Figure 86: Polyspace static verification report.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 189      |

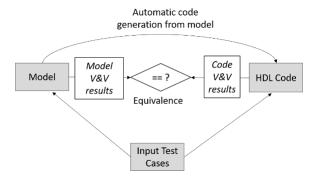

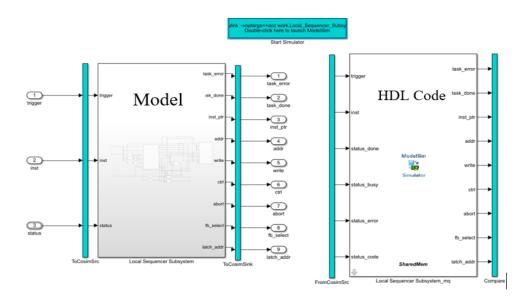

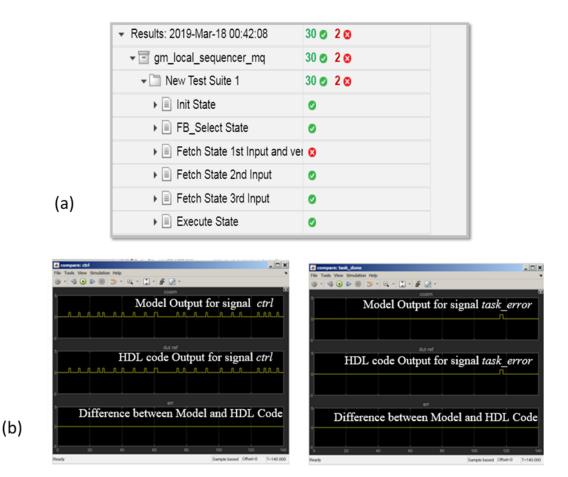

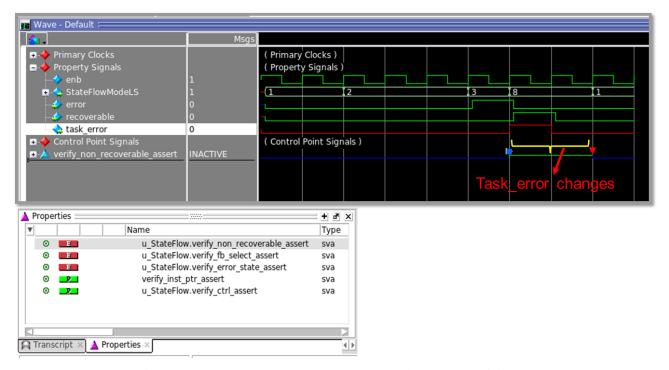

| Figure 87: Modelsim Co-simulation Equivalence Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 190      |